**这是本文档旧的修订版!**

脉冲发生器

====硬件平台====

====设计要求====

- 掌握Verilog子模块的调用

- 掌握PWM和脉冲发生的原理

- 基于STEP-Baseboard平台实现脉冲发生器的设计,周期可调,占空比可调

====工作原理====

脉冲发生器是信号发生器的一种,是周期和占空比均可调的矩形脉冲的发生器。

周期:在数字信号的领域中是信号变化的过程中,某段波形重复出现,其某一次开始至结束的这段时间就称为“周期“。

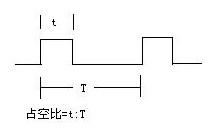

占空比:是在一串理想的脉冲系列中,正脉冲的持续时间与脉冲周期的比值。例如在下图中t为正脉冲的持续时间,T为脉冲周期,占空比为t/T。

脉冲发生一般通过对一个高频的脉冲信号进行分频来生成。

分频比:指方波的周期和高频信号手气之间发的比例关系,通过控制分频比来生成不同频率的方波。例如,开发系统上的时钟频率是25MHz,如果要生成5MHz的方波,则分频比为5。

====硬件连接====

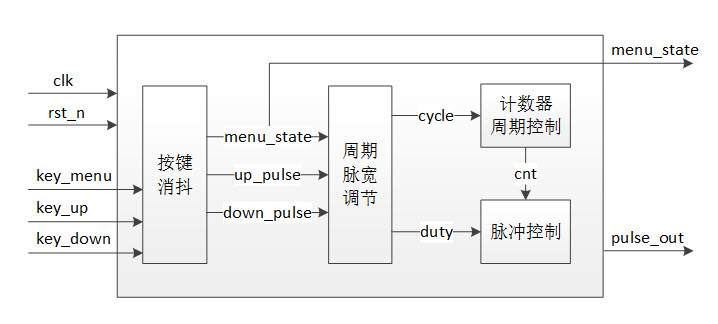

为了方便在硬件平台上演示,我们使用25MHz的系统时钟作为高频信号做分频处理,产生脉冲信号,通过调节脉冲信号的周期和正脉冲的宽度,最终生成我们需要的脉冲信号。

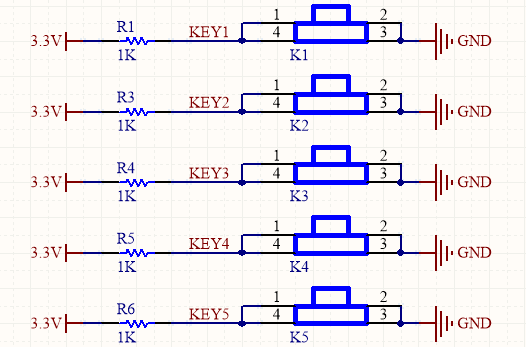

三路按键输入:

- keymenu:使用按键K5作为输入,按动K5按键控制周期和脉宽调节模式的切换。 * keyup:使用按键K1作为输入,按动K1按键根据所处的模式控制周期或脉宽参数的增加。

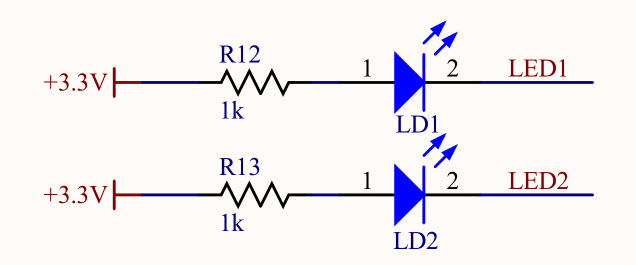

- keydown:使用按键K3作为输入,按动K3按键根据所处的模式控制周期或脉宽参数的减小。 两路LED输出: * menustate:使用小脚丫核心板上的LD1作为输出,当LED点亮或熄灭时分别表示脉宽调节模式或周期调节模式。

- pulse_out:使用小脚丫核心板上的LD2作为输出,可以根据LED的亮度表示周期和脉宽的变化(注意:当输出低电平时LED点亮)。

====代码设计====

设计文件

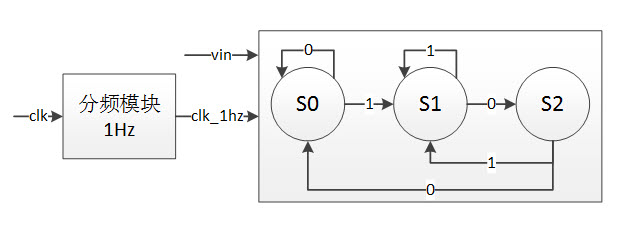

为了得到1Hz的信号,我们设计了25位的计数器cnt进行0.5s周期的循环计数,同时clk_1hz信号进行翻转,这样就得到了序列检测的时钟信号,然后再以序列检测的时钟信号为触发条件进行状态机的控制最终实现序列检测。

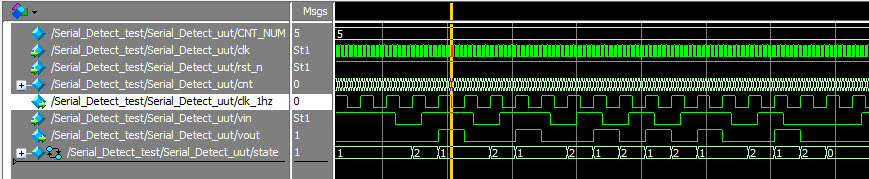

首先是计数器的设计,计数器的计数范围为0~CNTNUM-1,设计文件代码中我们定义参数CNTNUM为12500000,但是在仿真文件调用设计文件时,为了方便仿真,我们会将参数CNT_NUM重新赋值为5.

reg [24:0] cnt = 25'd0; always@(posedge clk or negedge rst_n) begin if(!rst_n) begin cnt <= 25'd0; clk_1hz <= 1'b0; end else if(cnt>=(CNT_NUM-1)) begin cnt <= 25'd0; clk_1hz <= ~clk_1hz; end else begin cnt <= cnt + 25'd1; end end

然后按照状态机的状态转移图实现状态机的设计。

reg[1:0]state; always @(posedge clk_1hz or negedge rst_n) begin if(!rst_n) begin state<=s0; vout<=0; end else case(state) s0: begin if(vin==0) begin state<=s0;vout<=0; end else begin state<=s1;vout<=0; end end s1: begin if(vin==0) begin state<=s2;vout<=0; end else begin state<=s1;vout<=0; end end s2: begin if(vin==0) begin state<=s0;vout<=0; end else begin state<=s1;vout<=1; end end default:state<=s0; endcase end

我们在设计中将序列检测的时钟信号设计为1Hz,并且使用LED指示序列检测的时钟信号的变化,方便在板子上按键及观察输出的情况。

测试文件

测试文件中我们需要对设计文件中的参数CNT_NUM进行重新赋值,同时对vin信号每400ns(序列检测时钟 = 系统时钟周期分配系数2 = 4052 = 400ns)间隔取随机值。

always vin = # 400 $random; wire clk_1hz,vout; Serial_Detect # ( .CNT_NUM(CNT_NUM) ) Serial_Detect_uut ( .clk(sys_clk), .rst_n(sys_rst_n), .vin(vin), .clk_1hz(clk_1hz), .vout(vout) );

引脚分配如下:

| 管脚名称 | clk | rstn | vin |clk1hz | vout | ||

|---|---|---|---|---|---|

| FPGA管脚 | C1 | A2 | B7 | A3 | A7 |

仿真结果

资源报告

| 资源 | 数量 | 比例 | 说明 |

|---|---|---|---|

| LUTs | 39 | 3% | |

| 寄存器 | 28 | 2% | |

| 存储器 | 0 | 0% | |

| IO管脚 | 5 | ||

| 时钟频率 | 25MHz |

知识点

- 分频设计

- 时序控制

- 简单状态机

参考文档

相关文档

| 文件名称 | 功能 |

|---|---|

| Serial_Detect.v | 流水灯 |

| Serial_Detect_test.v | 测试文件 |