Lattice的MachXO2系列FPGA的使用

在我们的学习系统中我们选用了Lattice Semiconductor公司的MachXO2系列FPGA,主要出于以下几方面的考虑:

在我们的学习系统中我们选用了Lattice Semiconductor公司的MachXO2系列FPGA,主要出于以下几方面的考虑:

- Lattice Semiconductor公司的FPGA学习和使用门槛最低,易学易用

- 性价比高,除了适合入门级的学习之用,还能够满足80%以上的企业应用

- 非常适合于高校教学实验及创新实践

本节我们来看看我们选用的这个系列的FPGA有哪些特点以及应用领域。

硬件部分

1 MachXO2 FPGA硬件特性

- 灵活的逻辑架构,256-6864个查找表(LUTs),18-334个输入输出管脚(PIOs)

- 超低功耗 - 采用先进的65nm低功耗工艺,等待状态时功耗低至22μW,具有可编程、低摆动的差分I/O

- 最高达334个hot-socketable输入/输出管脚避免额外的泄漏

- TransFR特性允许在现场设计更新而不干扰设备的运行

- 可编程sysIO™ 支持LVCMOS, LVTTL, PCI, LVDS, BLVDS, MLVDS, RSDS, LVPECL, SSTL, HSTL以及更多中接口,可编程上拉、下拉模式

- 灵活的片上时钟处理 - 8个主时钟输入管脚、支持高速I/O的双沿时钟、每个器件内有2个模拟PLL、外部时钟输入时频率范围从7MHz到400MHz

- 芯片内有5.5%精度的片上振荡器

- 每颗芯片都有TraceID进行追踪

- 最小封装为2.5mmx2.5mm

2 XO2 FPGA的结构

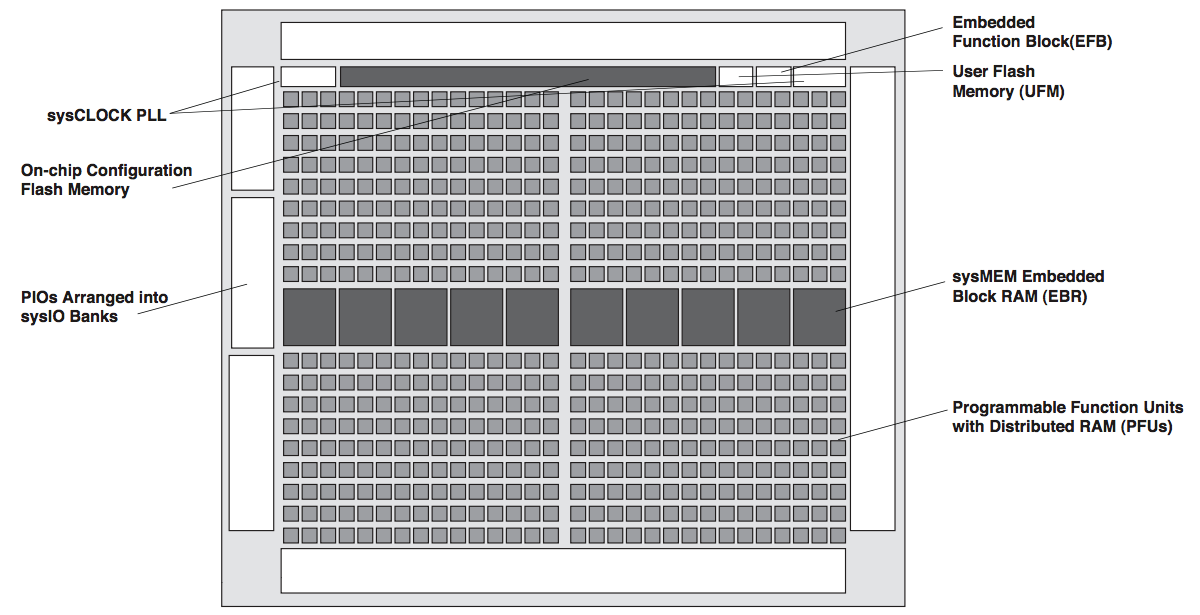

MachXO2内部结构功能

可编程部分:

- FPGA的核心部分是由逻辑门(Logic Gate)、寄存器(Register)以及连线(Wire)构成的可编程的逻辑块,也即此图中的PFUs(Programmable Function Units with Distributed RAM - 带分布式存储器的可编程功能单元),这些逻辑块的规模由两个重要指标表示LUTs和Slices

- 可编程输入输出管脚PIOs:分成多个Bank的sysIO,每个Bank可以有单独的供电电压Vccio,以支持不同电平的数据传输协议,这些输入输出管脚可以自由分配,并可以通过编程、配置支持多种数据传输协议(不同电平、差分等),IO管脚的输入输出电阻也可以编程、配置

- 块RAM:在这里称为sysMEM Embedded Block RAM(EBR)

硬核部分: 当今的FPGA除了可编程的逻辑和IO之外,还提供了一系列常用的功能模块,以硬核的方式内嵌在芯片以内,即便用户在设计中不用这些功能,这些资源也存在于系统中。硬核化的优势在于速度快、功耗低,且这些硬核一般为常用的功能块。在MachXO2中内嵌的硬核功能主要有:

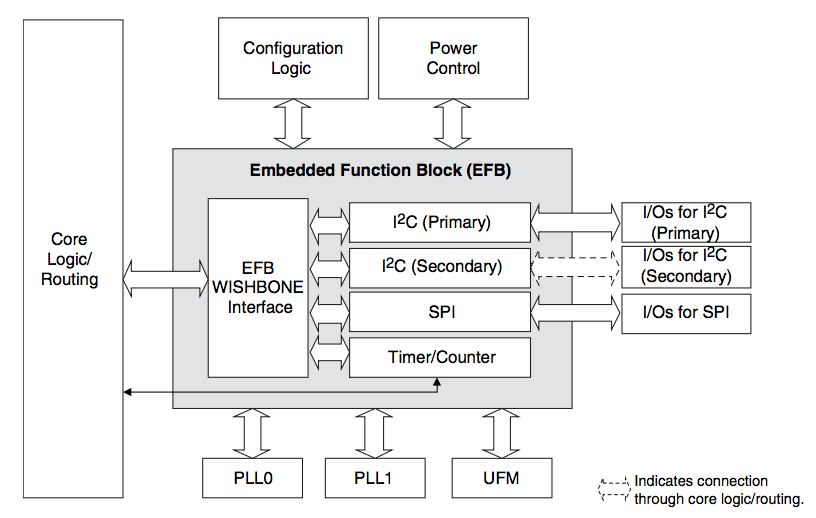

- 嵌入式功能块:Embedded Function Blocks(EFB)- MachXO2主要的EFB包括一个SPI、两个I2C、和一个定时器

- 程序Flash:On-chip Configuration Flash Memory

- 用户Flash:User Flash Memory(UFM)

- PLL/DLL: sysPLL

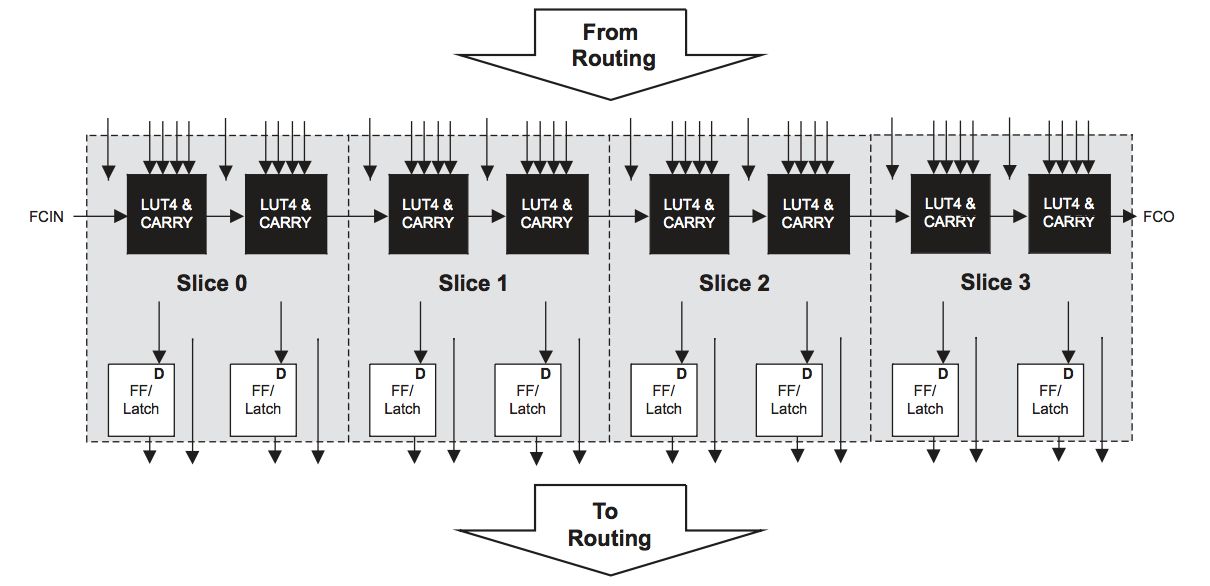

MachXO2内部的可编程功能单元构成示意图

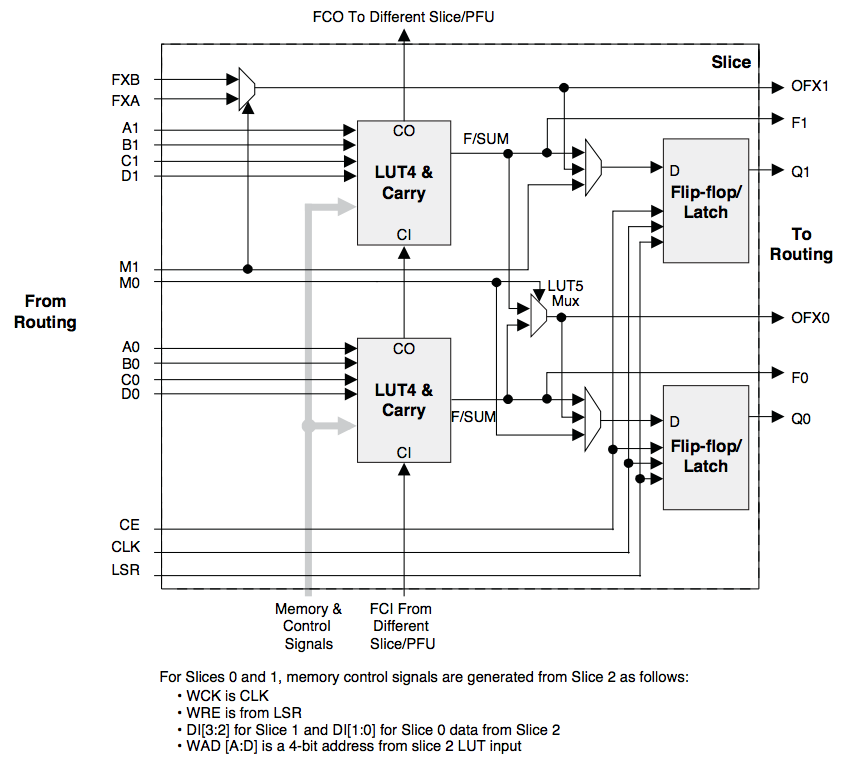

MachXO2的Slice构成示意图

MachXO2内部的嵌入式功能模块

3 XO2 FPGA的资源

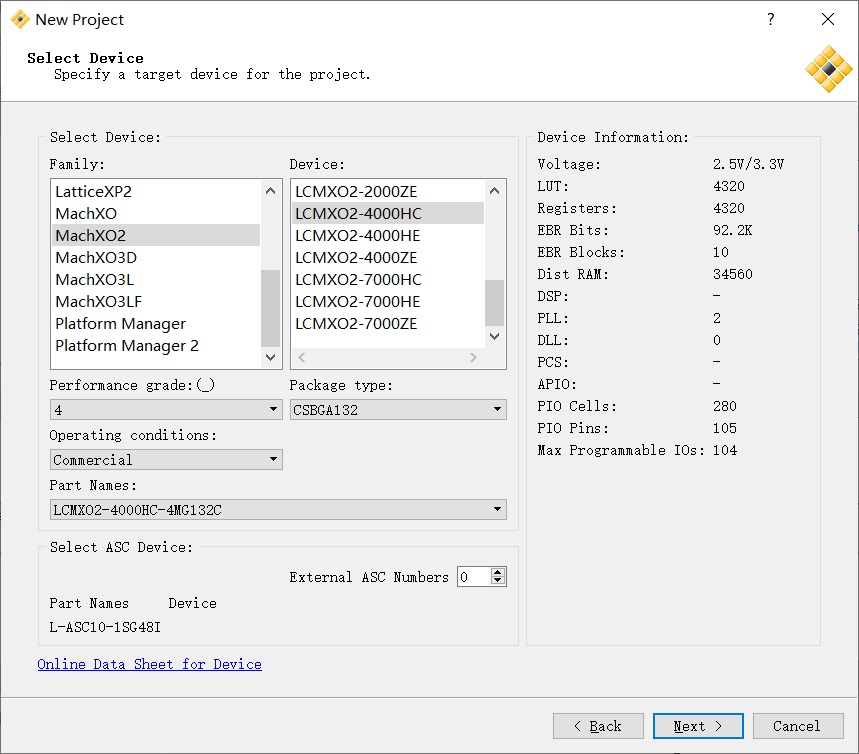

上面我们介绍了MachXO2内部的结构,XO2系列不同的型号内部结构是相同的,但资源的多少则取决于所选择的型号,在设计中我们需要根据资源的需求来选用合适的器件,了解到这些器件的资源配置对于我们设计也是有帮助的,可以充分利用器件内部的资源简化外围电路的设计,同时也要知道器件内部的局限性,在外围进行扩展。在我们小脚丫2.0版本中我们选用了XO2-4000的型号(参见MachXO2选型表),它具有如下资源:

- 4320个查找表

- 10个嵌入式RAM块,攻击92kbits的容量

- 34kbits的分布式SRAM

- 96Kbits的用户Flash存储器

- 支持DDR/DDR2/LPDDR存储器接口

- 内部具有配置用的Flash

- 支持双启动模式

MachXO2 选型表

| O2-256 | XO2-640 | XO2-640U | XO2-1200 | XO2-1200U | XO2-2000 | XO2-2000U | XO2-4000 | XO2-7000 | |

| 查找表(LUTs)的密度 | 256 | 640 | 640 | 1280 | 1280 | 2112 | 2112 | 4320 | 6864 |

| EBR RAM块(9 Kbits/block) | 0 | 2 | 7 | 7 | 8 | 8 | 10 | 10 | 26 |

| EBR SRAM(Kbits) | 0 | 18 | 64 | 64 | 74 | 74 | 92 | 92 | 240 |

| Dist. SRAM (Kbits) | 2 | 5 | 5 | 10 | 10 | 16 | 16 | 34 | 54 |

| 用户Flash存储(Kbits) | 0 | 24 | 64 | 64 | 80 | 80 | 96 | 96 | 256 |

| PLL + DLL | 0 | 0 | 1 + 2 | 1 + 2 | 1 + 2 | 1 + 2 | 2 + 2 | 2 + 2 | 2 + 2 |

| 支持DDR/DDR2/LPDDR存储器 | - | - | Yes | Yes | Yes | Yes | Yes | Yes | Yes |

| 配置存储器 | 内部Flash | ||||||||

| 双启动 | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes |

| 内嵌功能块 | I2C (2), SPI (1), Timer (1) | ||||||||

| 内核电压Vcc 1.2 V | ZE | ZE | - | ZE | - | ZE & HE | HE | ZE & HE | ZE & HE |

| 内核电压Vcc 2.5 - 3.3 V | HC | HC | HC | HC | HC | HC | HC | HC | HC |

4 主要应用领域

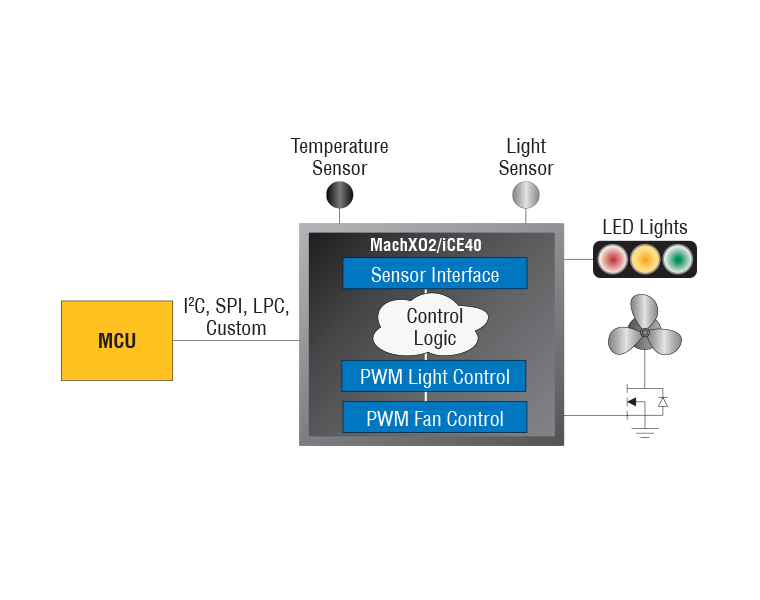

4.1 微处理器的接口扩展

4.2 提高实时性要求较高的功能的性能

- 在系统上电时通过快速启动逻辑精确地控制信号

- 可以配置PWM功能以精确产生照明和马达控制所需要的模拟电压

- 构建传感器缓冲器以及智能中断以保证实时世界的事件能够被捕捉

- 采用硬件UART克服采用软件实现UART的性能限制

4.3 通过硬件加速提高系统的性能

设计工具及设计流程

1 Lattice Diamond集成化开发环境

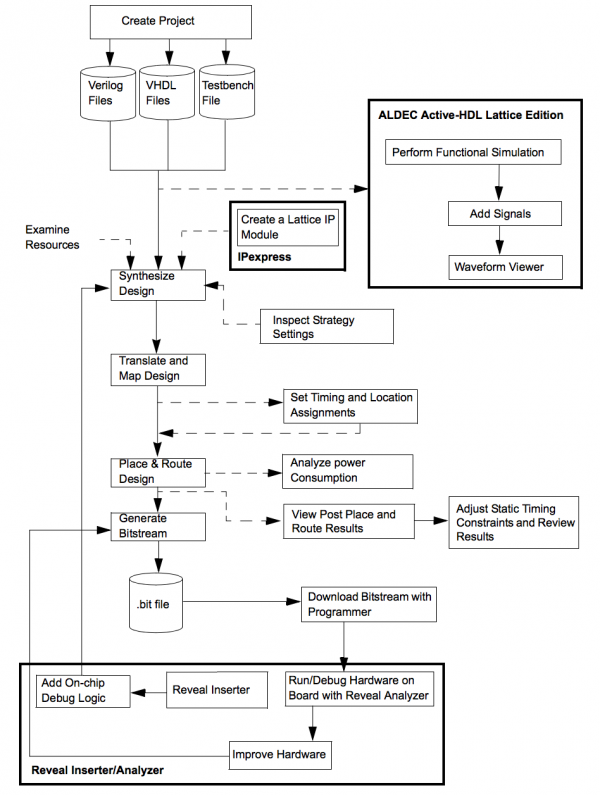

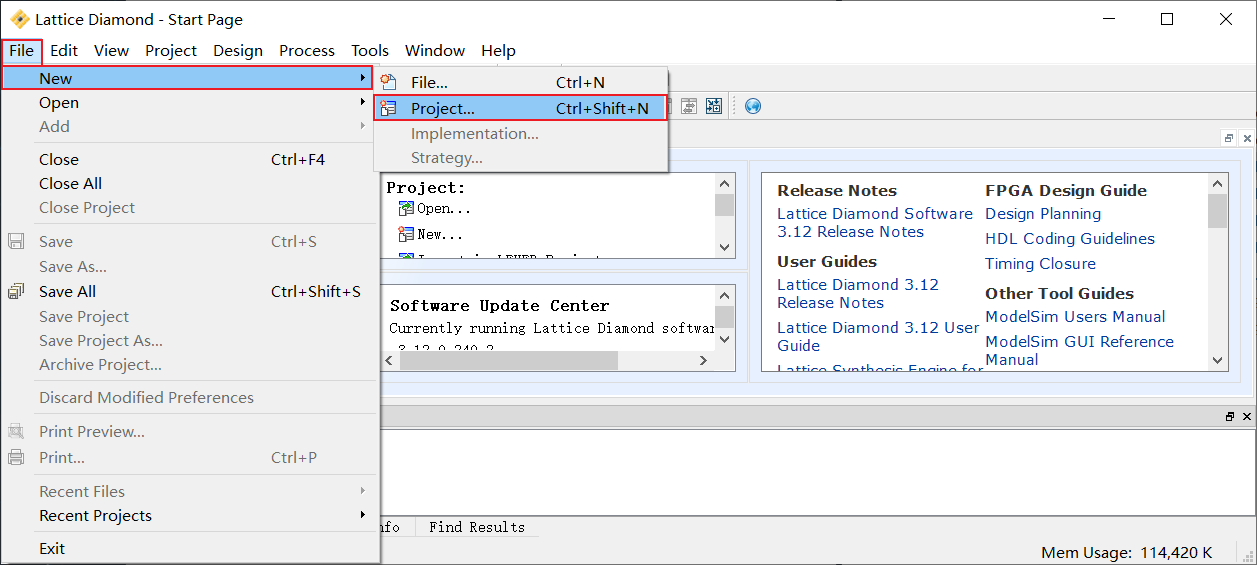

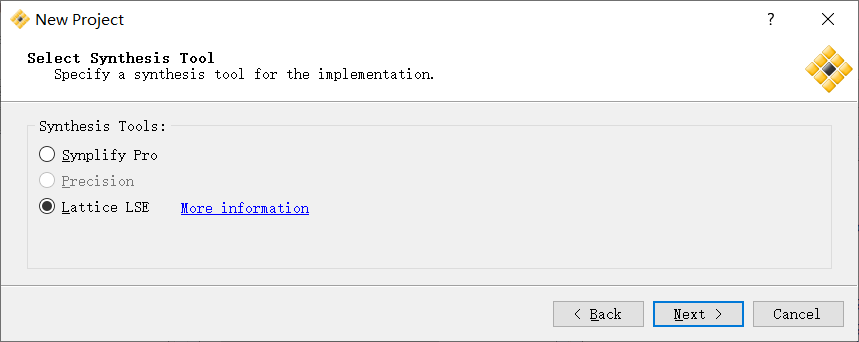

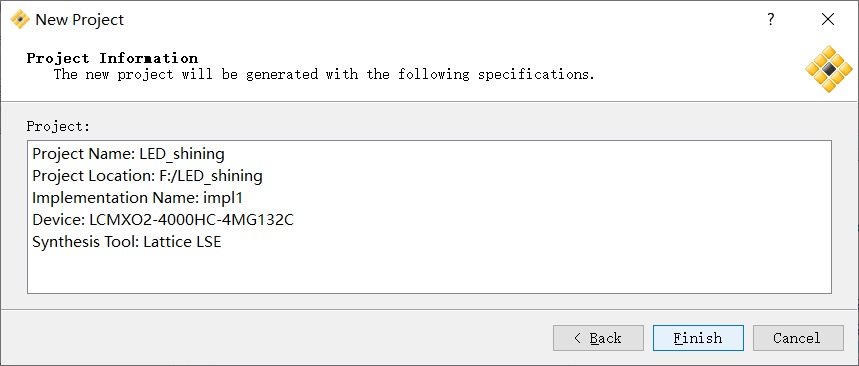

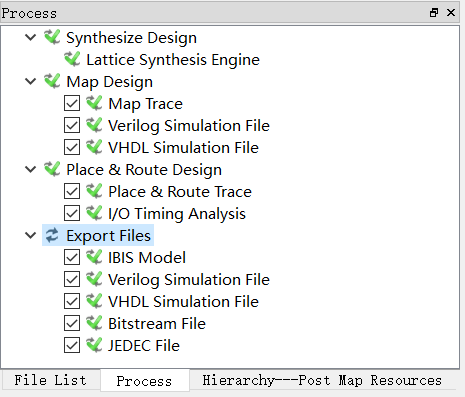

参考Diamond安装及配置安装好Diamond,如果遇到问题可以先看看Diamond安装常见问题解答。现在我们就可以使用Diamond软件开始FPGA的设计了,整个设计流程参照下图。

采用Diamond设计FPGA逻辑的基本流程

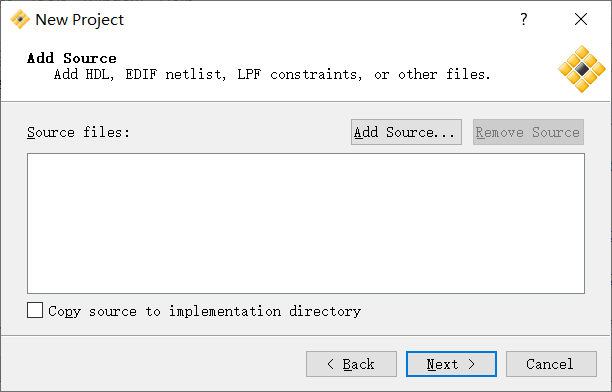

2 运行第一个例程

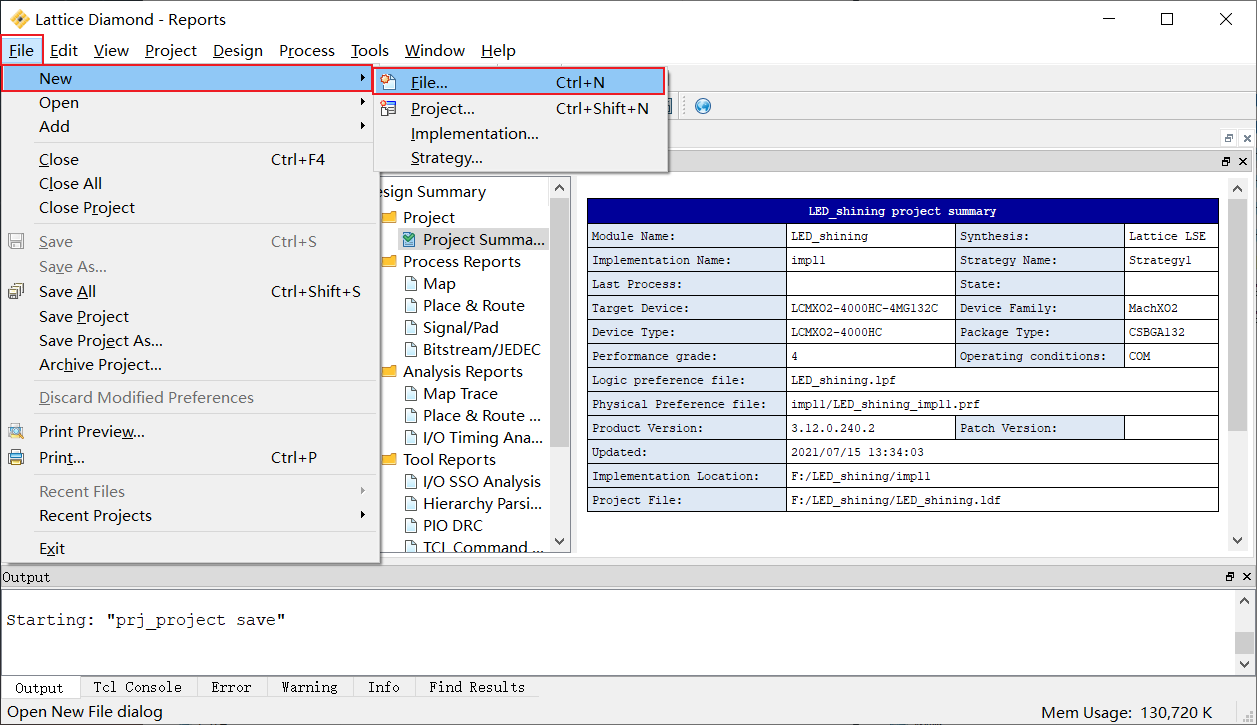

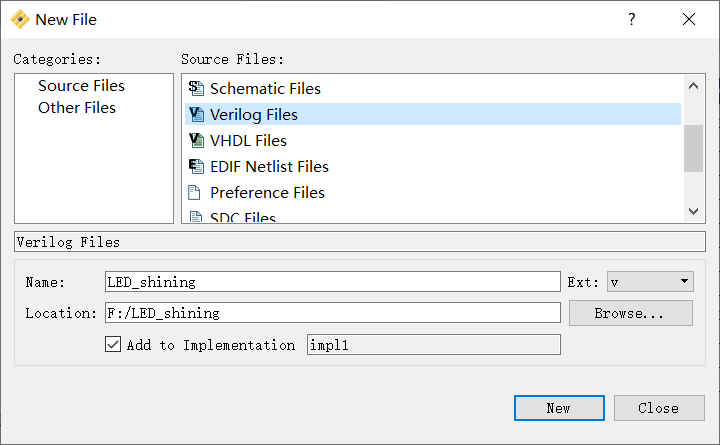

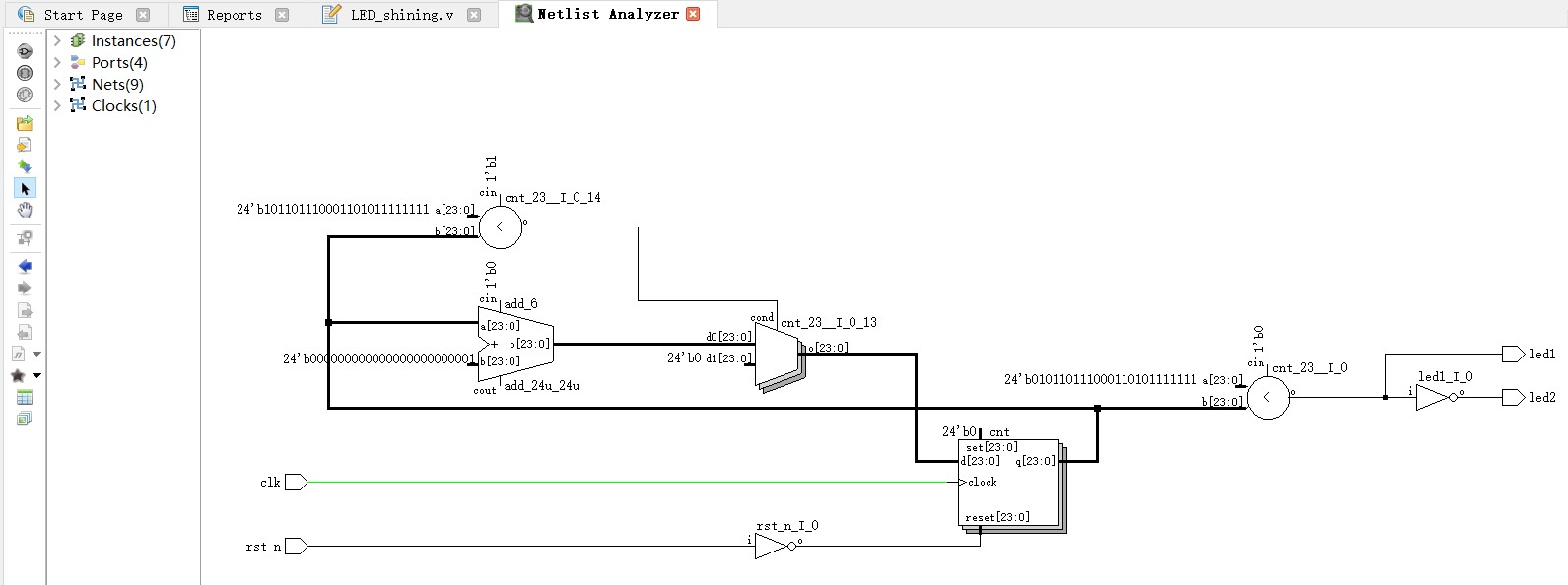

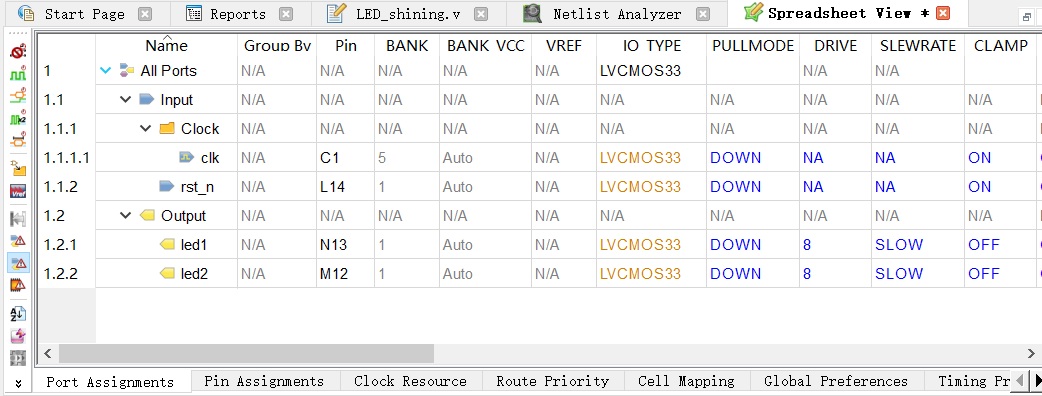

下面我们可以开始可编程逻辑的开发,我们以控制LED交替闪烁为例,完成自己的第一个程序:

- 程序源码已经准备好,如下,将代码复制到设计文件LED_shining.v中,并保存。

module LED_shining ( input clk, //clk = 12mhz input rst_n, //rst_n, active low output led1, //led1 output output led2 //led2 output ); parameter CNT_1S = 12_000_000 - 1; //time 1S parameter CNT_05S = CNT_1S >> 1; //time 0.5S reg [23:0] cnt; always @(posedge clk or negedge rst_n) begin if (!rst_n) cnt <= 1'b0; else if (cnt >= CNT_1S) cnt <= 1'b0; else cnt <= cnt + 1'b1; end wire clk_div = (cnt>CNT_05S)? 1'b1 : 1'b0; assign led1 = clk_div; assign led2 = ~clk_div; endmodule

到这里完成了第一个程序流文件的生成,下面可以下载到FPGA中。

3 工程仿真

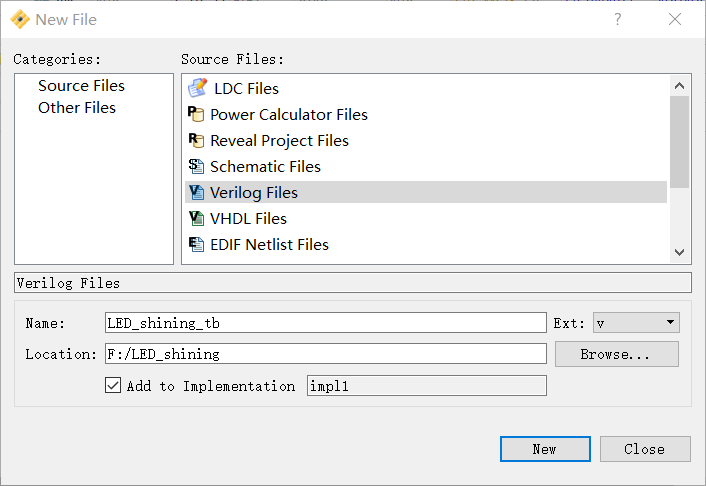

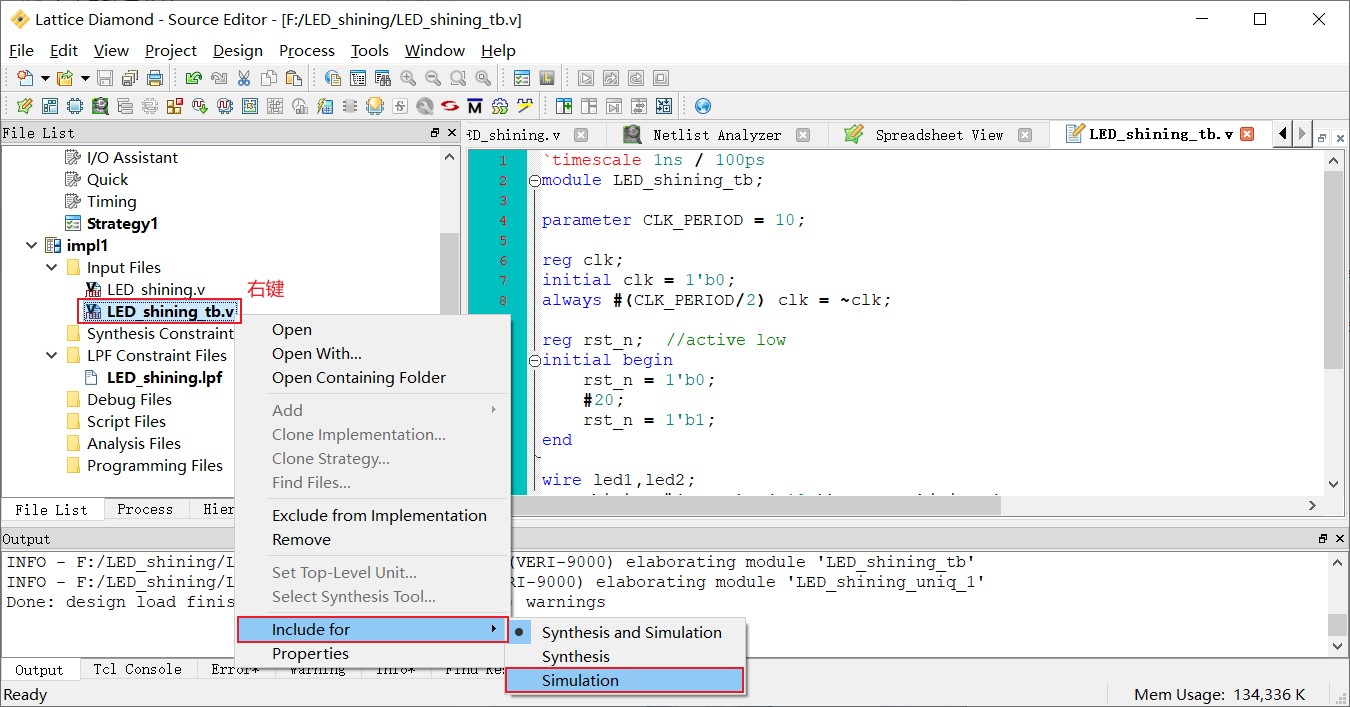

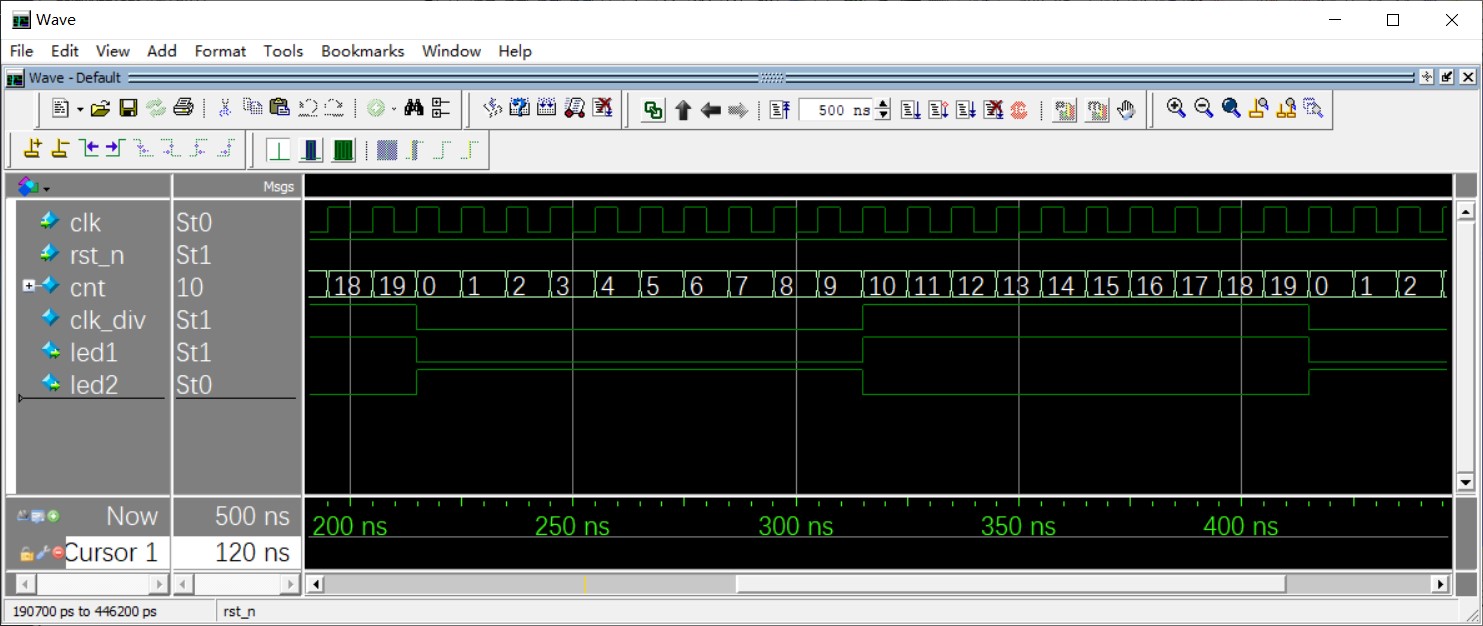

上面我们走了整个工程开发的过程,例程较为简单,对于复杂的工程开发需要预仿真和后仿真等,保证最终的程序设计逻辑和时序符合我们的设计要求。 仿真软件很多,这里我们使用软件自带的Modelsim软件进行功能仿真:

- 测试源码如下,复制到LEDshiningtb.v文件并保存。为了方便仿真,我们在LEDshiningtb.v调用LEDshining模块时将CNT1S重新赋值为19:

`timescale 1ns / 100ps module LED_shining_tb; parameter CLK_PERIOD = 10; reg clk; initial clk = 1'b0; always #(CLK_PERIOD/2) clk = ~clk; reg rst_n; //active low initial begin rst_n = 1'b0; #20; rst_n = 1'b1; end wire led1,led2; LED_shining #(.CNT_1S ( 19 )) u_LED_shining ( .clk ( clk ), .rst_n ( rst_n ), .led1 ( led1 ), .led2 ( led2 ) ); endmodule

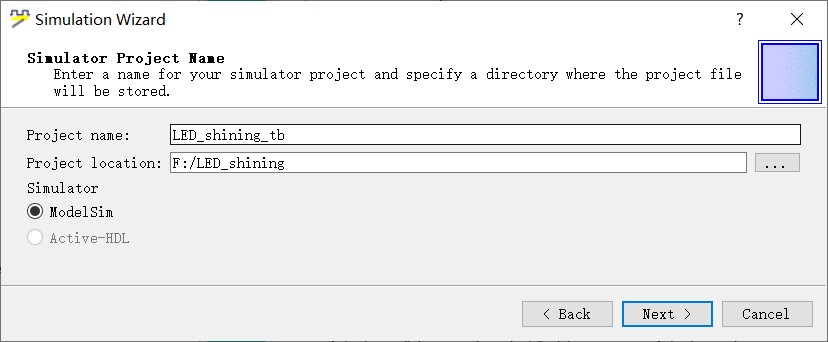

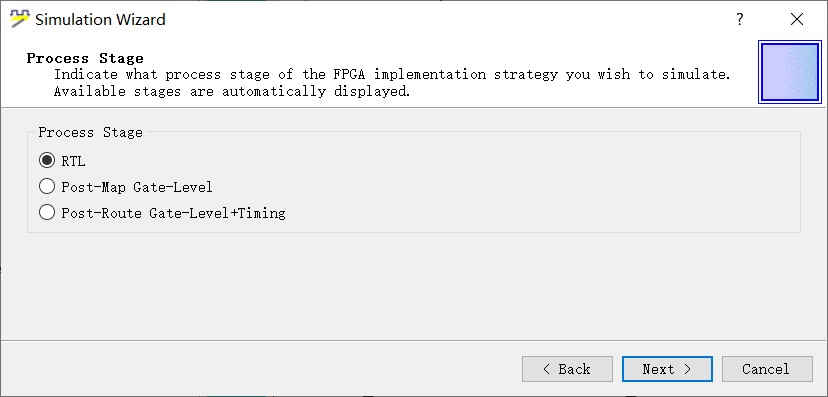

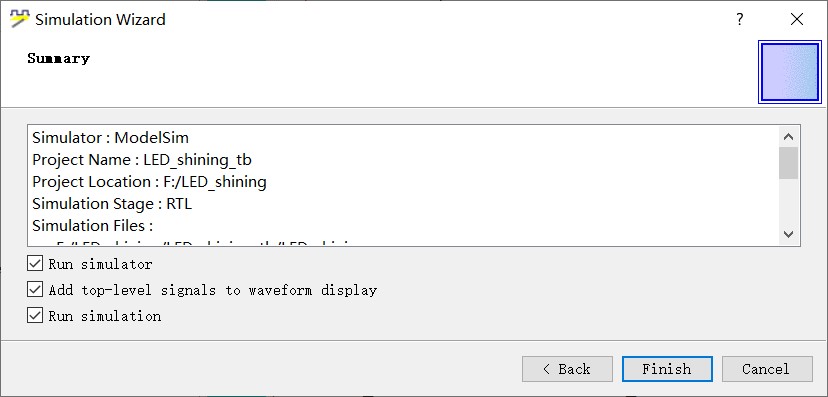

- 准备工作完成,我们选择Tools →SimulationWizard →Next,

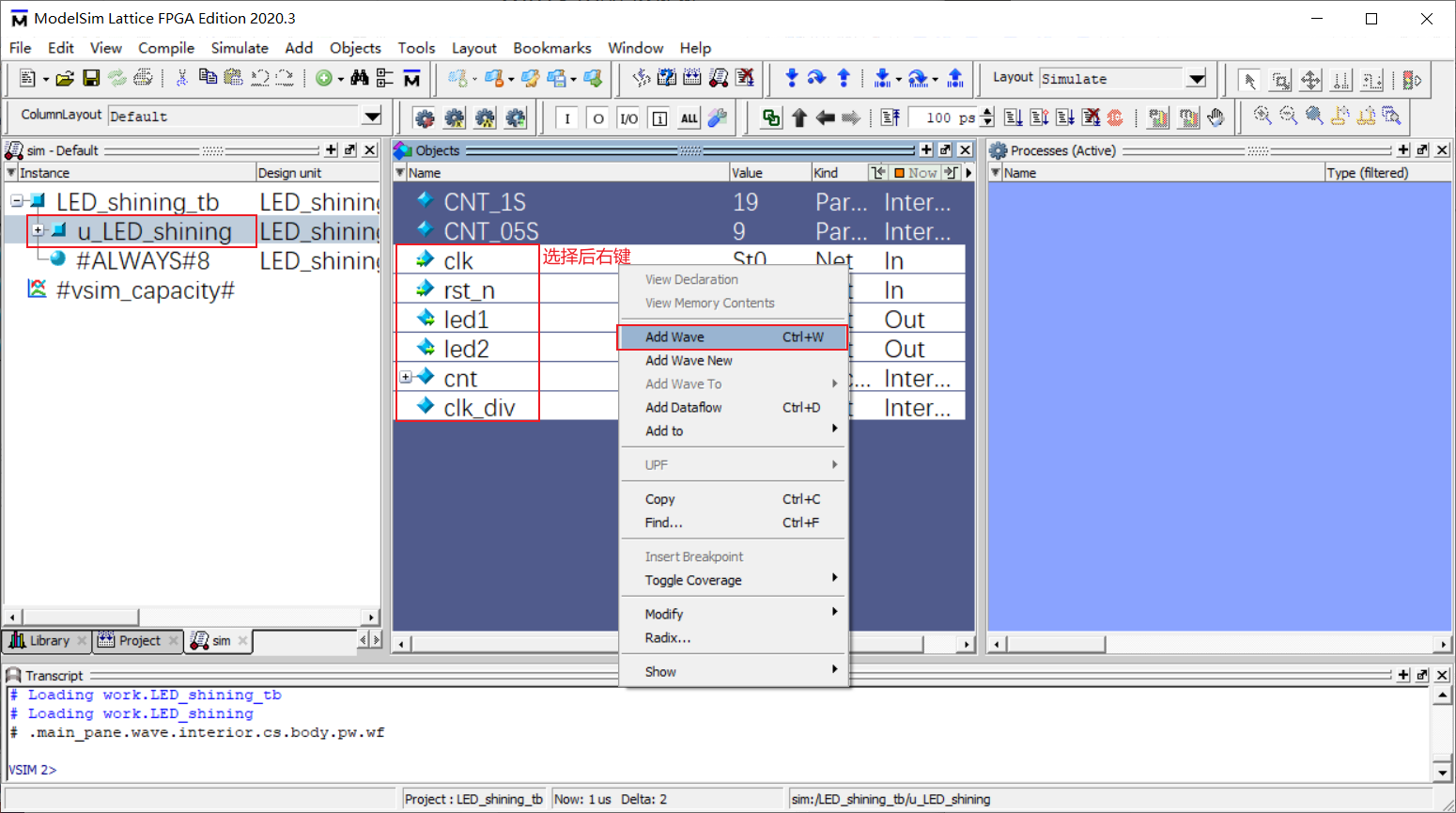

- ModelSim软件启动,可以直接查看testbench文件中变量的时序变化,想要看LED_shining模块中的变量的时序,可以通过下图中的步骤添加信号至WAVE窗口。

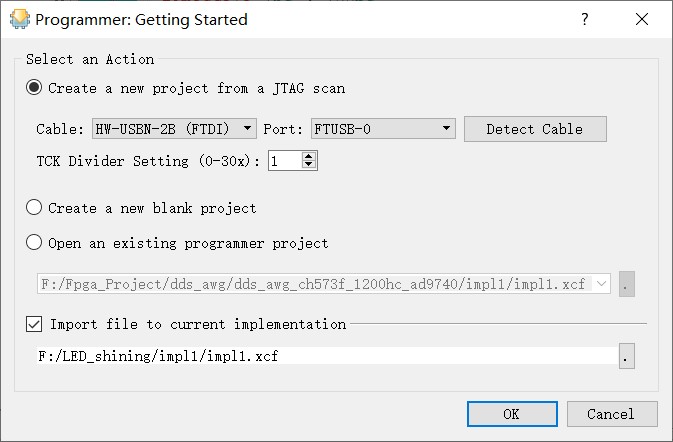

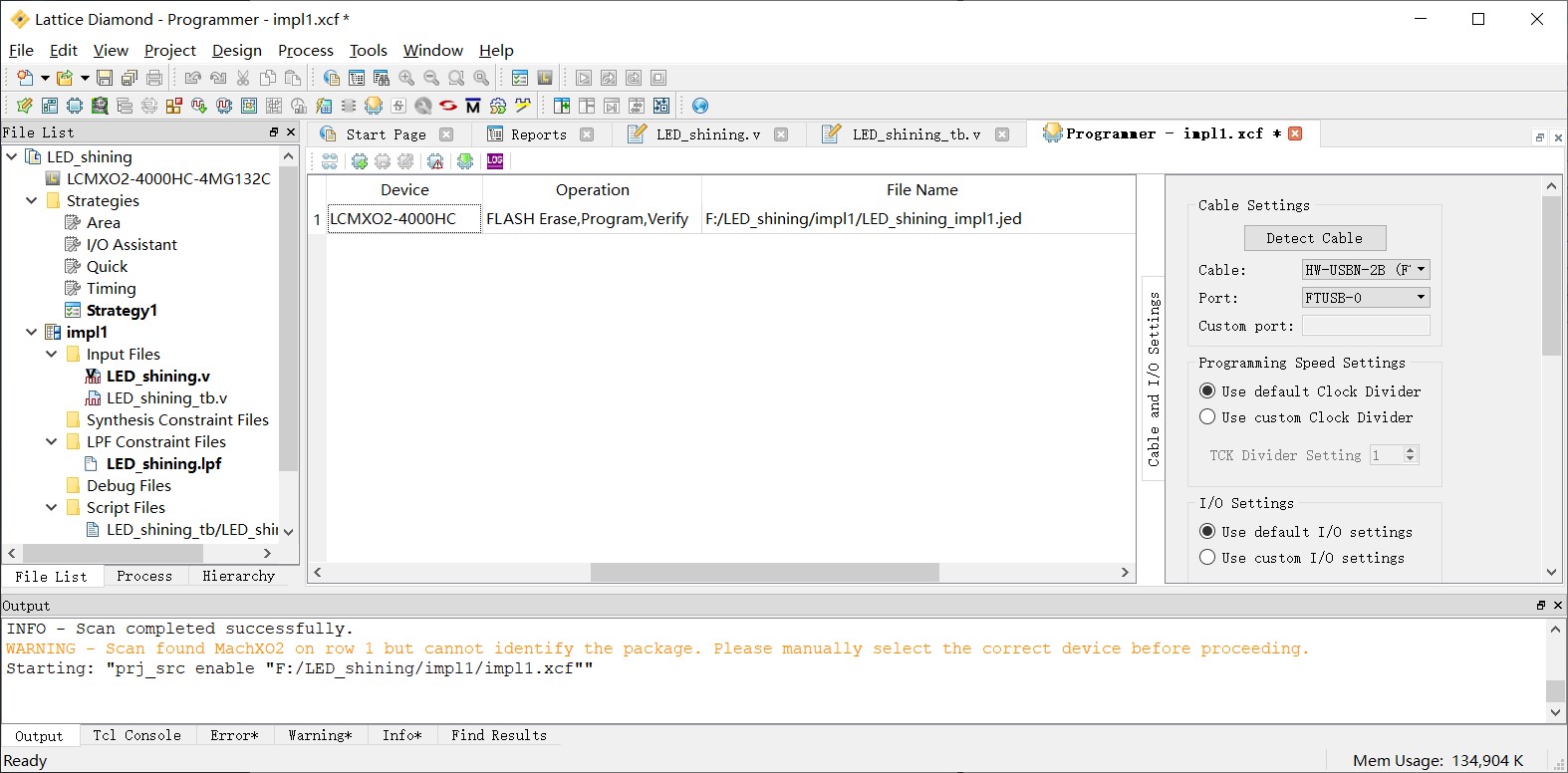

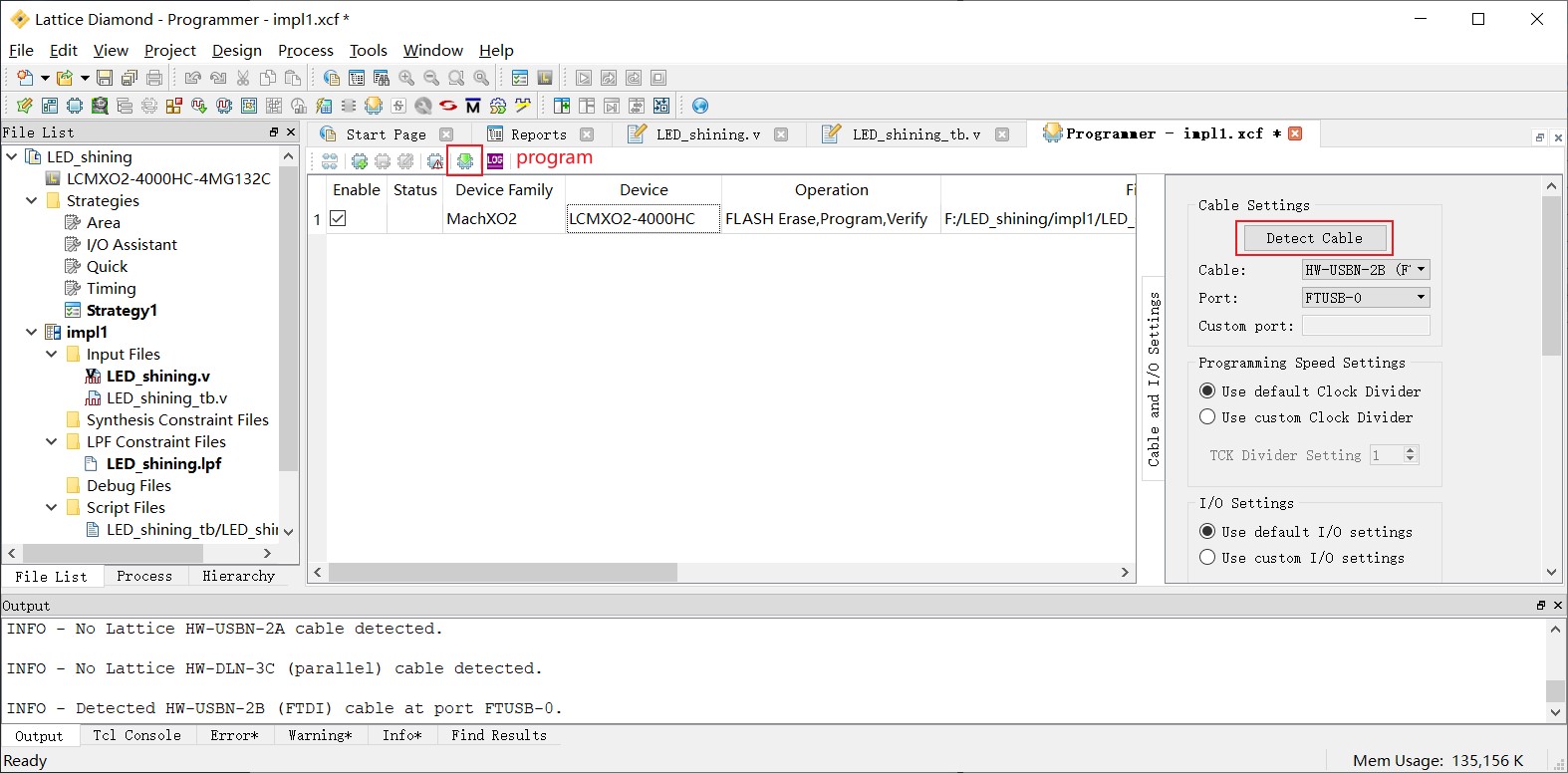

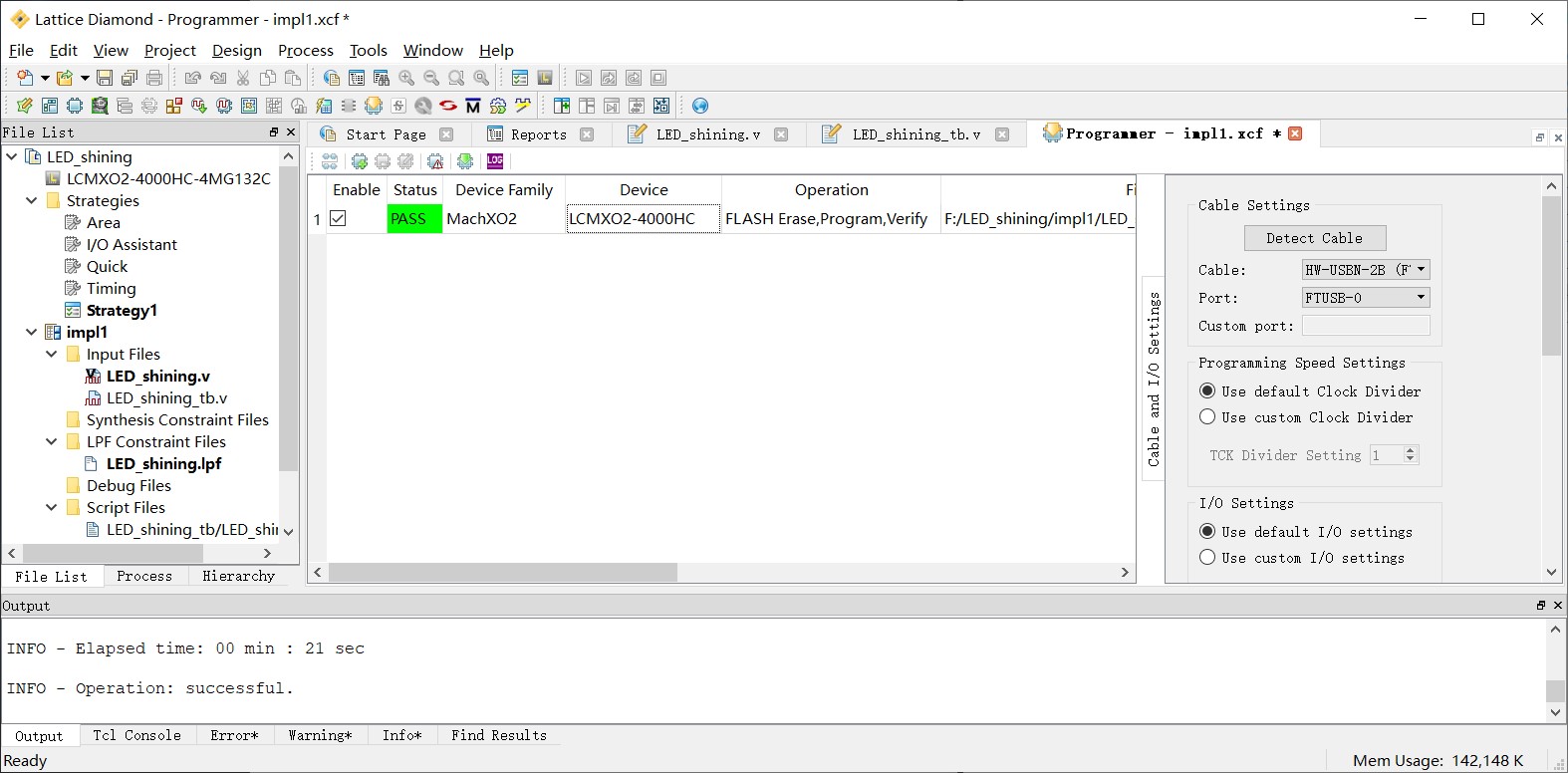

4 下载程序到FPGA

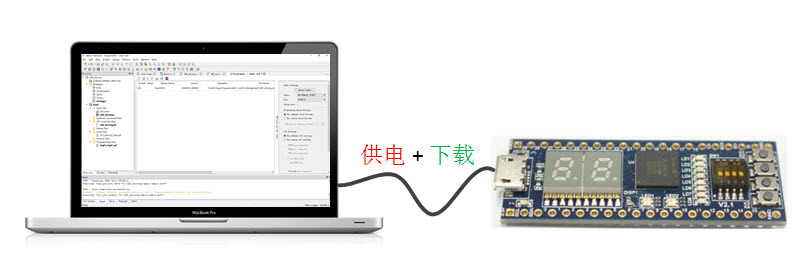

STEP MXO2 V2的编程芯片已经集成到小脚丫开发板上,因此只需要一根Micro USB线和电脑相连,就可以完成供电和编程的功能,驱动安装好以后就可以开始编译下载程序了。 将编译完成的程序下载到开发板:

5 STEP MXO2入门教程

到这里我们了解了用Diamond软件进行开发的完整流程。接下来我们开始STEP-MXO2入门教程一步一步进入可编程逻辑设计。