2.3.3 FSM(有限状态机):序列1101识别器

这是由五个练习组成的系列中的第二个组件,旨在通过几个小型电路构建一个复杂的计数器。关于整体设计,请参阅2.3第6小结。

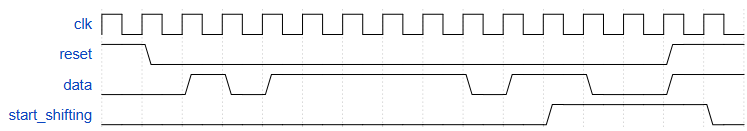

构建一个有限状态机(Finite-state machine, FSM),用于在输入的比特流中搜索序列1101。当找到该序列时,应设置start_shifting为1,并保持这一状态直到复位。卡在最终状态是为了模拟进入一个尚未实现的更大FSM中的其他状态。我们将在接下来的几个练习中扩展这个FSM。

模块声明

module top_module (

input clk,

input reset, // Synchronous reset

input data,

output start_shifting);