30.Q2a: 有限状态机1(FSM)

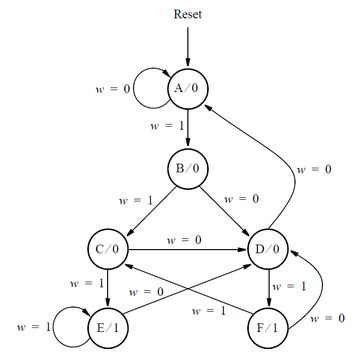

考虑下面所示的状态图。

编写完整的Verilog代码来表示这个FSM(有限状态机)。按照讲座中的做法,为状态表和状态触发器分别使用独立的always块。使用连续赋值语句或一个always块(根据你的判断)来描述FSM的输出,该输出称为z。你可以自由地分配任何你希望使用的状态码。

模块声明

module top_module (

input clk,

input reset, // Synchronous active-high reset

input w,

output z

);