16.检测两边沿(同时检测上升沿和下降沿)

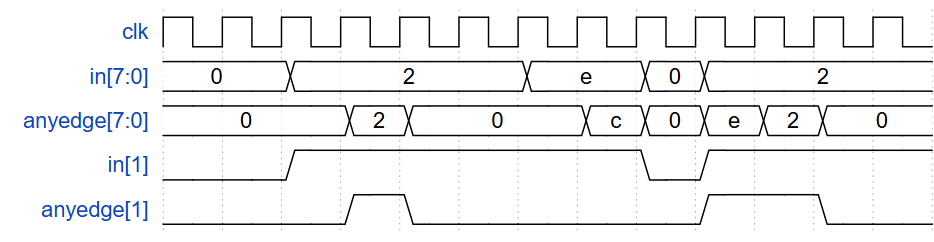

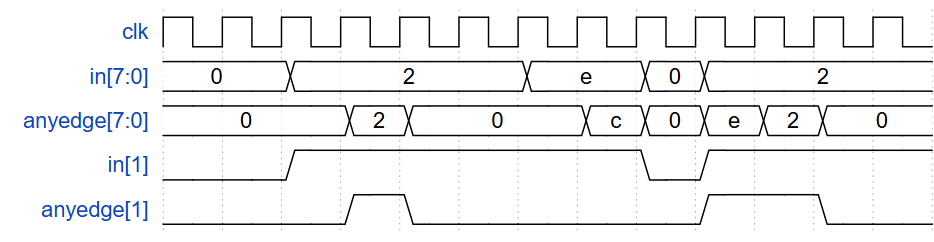

对于8位向量中的每一个位,检测输入信号何时从一个时钟周期到下一个周期发生变化(即检测任一跳变沿)。当发生从0到1的转换时,输出位应该在变化发生后的下一个周期被置位。

以下是一些示例。为了清晰起见�,单独展示了in[1]和anyedge[1]的情况。

模块声明

module top_module (

input clk,

input [7:0] in,

output [7:0] anyedge

);

对于8位向量中的每一个位,检测输入信号何时从一个时钟周期到下一个周期发生变化(即检测任一跳变沿)。当发生从0到1的转换时,输出位应该在变化发生后的下一个周期被置位。

以下是一些示例。为了清晰起见�,单独展示了in[1]和anyedge[1]的情况。

模块声明

module top_module (

input clk,

input [7:0] in,

output [7:0] anyedge

);