数字秒表电路

本文描述了数字秒表电路的原理、设计和操作。数字秒表可以是一个显示实际时间(分钟、小时和秒)的电路,也可以是一个显示时钟脉冲数量的电路。这里我们设计第二种类型的电路,其中电路显示从 0 到 59 的计数,表示 60 秒的时间间隔。换句话说,这里电路仅显示秒数。该电路由一个 555 定时器产生时钟脉冲和两个计数器 IC 执行计数操作组成。

1. 数字秒表电路原理

该电路基于两级计数器操作原理,采用同步级联方式。其思想是显示�从 0 到 59 的时钟脉冲计数,表示 60 秒的时间间隔。通过使用一个 555 定时器 IC 以非稳态模式连接,产生每秒一次的时钟脉冲。第一个计数器从 0 计数到 9,当第一个计数器的计数值达到 9 时,第二个计数器开始计数操作。计数器 IC 以级联方式连接,每个计数器的输出连接到用于驱动七段显示器的 BCD 到七段解码器。

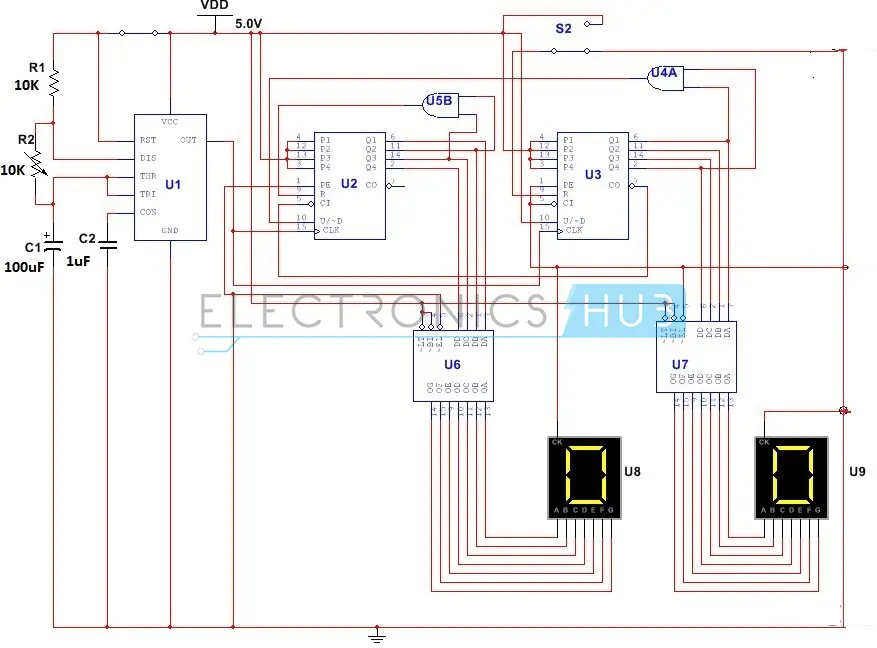

2. 数字秒表电路图

3. 数字秒表电路设计

3.1 555 定时器的设计

设计的第一部分涉及设计 555 定时器的非稳态多谐振荡器。所需的时间周期为 1 秒。输出信号的频率由公式 给出,我们可以计算出 C 的值,假设 Ra 和 Rb 的值约为 10K。这里我们得到一个 100uF 的电解电容器。

3.2 计数器 IC 的连接

设计的第二部分涉及将两个计数器 IC(4510)以同步级联方式连接。这是通过将计数器 IC 的时钟引脚连接到 555 定时器的输出,产生并行时钟输入信号来实现的。一个 IC 的进位输出引脚连接到另一个 IC 的进位输入引脚。

由于我们的目标是在第一个计数器计数到 9 时启动第二个计数器,我们通过设计一个简单的组合逻辑电路来实现这一点。根据计数器的真值表,对于计数值 9,对应的二进制计数或状态为 1001。换句话说,对于计数值 9,Q1 和 Q4 为高逻辑信号。这里我们使用一个与门 IC(7408),其输入连接到第一个计数器的 Q1 和 Q4 引脚,输出连接到第二个计数器的 U/D 引脚。

3.3 显示电路的设计

设计的第三部分涉及设计显示电路。通过将每个计数器 IC 的输出连接到 BCD 到七段解码器的输入来实现。每个解码器 IC(4511)的输出连接到七段显示器。

4. 数字秒表电路的工作原理

电路操作在常开开关被切换到闭合位置后开始。555 定时器产生高低信号,频繁地在间隔时间内切换,产生的振荡信号频率基于两个电阻器和充电电容器的值。换句话说,555 定时器 IC 产生所需时间周期的时钟脉冲。该时钟信号被馈送到 BCD 计数器 CD4510 的两级级联结构中。IC CD4510 包含四个同步时钟的 D 型触发器,这些触发器连接在一起以实现计数操作。时钟脉冲被两个 CD4510 计数器的两级同步级联结构计数。当 IC U3 接收到时钟脉冲时,它开始从 0 计数到 9。一旦计数达到 9,与门 IC U4A 产生高逻辑输出,该输出被馈送到 IC U2 的 U/D 引脚。IC U2 开始计数操作。IC U2 继续其计数操作,每当 U3 达到其结束计数时,U3 也继续计数。

5. 数字秒表的应用

-

用于时间测量和计时

-

适用于实验室、体育活动和其他需要精确计时的场合

6. 数字秒表的局限性

- 该电路仅显示秒数,无法显示分钟和小时

- 需要外部电源供电