BCD 到 7 段 LED 显示译码器电路

最常见的七段显示器用于显示数字,例如数码手表、计算器、时钟、测量仪器和数字计数器等。通常,LED 与 LCD 段提供数字与字符的显示输出。

然而,为了显示字符与数字(生成十进制读数),七段显示器最为常用。通常,这些显示器由数字 IC 的输出级驱动(如锁存器和十进制计数器等),以执行视觉指示。

但这些输出采用 4 位二进制编码十进制(BCD)格式,不适合直接驱动七段显示器。

使用显示译码器将 BCD 或二进制代码转换为适合七段显示的代码。通常具有 4 条输入线和 7 条输出线。在此,我们使用逻辑门设计一个简单的显示译码器电路。

尽管市面上有现成的 BCD 到 7 段译码器,但使用逻辑门设计译码器从经济性和知识性角度来看可能更有益。

1. 显示译码器电路原理

基本思路为使用组合逻辑电路驱动共阴极七段 LED 显示器。该逻辑电路设计有 4 个输入和 7 个输出,每个输出对应显示 IC 的一个输入。使用卡诺图(Karnough’s map)设计每个显示输出的逻辑电路。

2. 电路理论基础

首要方面是译码器。译码器是一种组合电路,用于将二进制或 BCD(Binary Coded Decimal)数转换为相应的十进制数。可以是简单的二进制到十进制译码器,也可以是 BCD 到七段译码器。

另一相关部分是组合逻辑电路。组合逻辑电路由逻辑门构成,仅包含输入与输出。其输出仅取决于当前输入状态。典型例子包括编码器与译码器、多路复用器、反向多路复用器、加法器、减法器等。

为理解这些逻辑电路的设计与运行,需要掌握布尔代数与逻辑门知识。例如应遵循互补律、结合律、德·摩根定律等布尔代数基本规则。

七段 LED 显示器由 8 个 LED 组成,其结构如“H”形排列。可分为共阳或共阴类型。共阴七段显示器具有 8 个引脚——7 个为 ‘a’ 到 ‘g’ 的输入引脚,第八脚为公共接地引脚。

3. 7 段显示译码器电路设计

步骤 1:首先分析共阴七段显示器。七段显示器由“H”型排列的 LED 组成。构建真值表,列出每个十进制数字的输入组合。例如数字 1 对应点亮 b 和 c 段。

步骤 2:构建真值表,列出 7 个显示输入信号、十进制数字及相应的 4 位二进制数字。

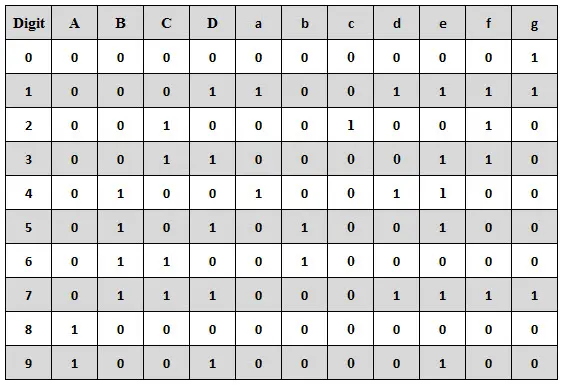

3.1 BCD 到 7 段译码真值表

译码器设计的真值表取决于显示器类型。如前所述,对于共阴七段显示器,译码器输出(段驱动)必须为高电平以点亮段。

下图展示共阴显示的 BCD→7 段译码真值表;表中列出了 7 个输出列,对应每一段。

假设段 a 的列显示其点亮的组合。因此,a 段在数字 0、2、3、5、6、7、8 和 9 时为激活状态。

从上述真值表中,可以写出每个输出功能的布尔表达式:

a = F₁(A, B, C, D) = ∑m (0, 2, 3, 5, 7, 8, 9)

b = F₂(A, B, C, D) = ∑m (0, 1, 2, 3, 4, 7, 8, 9)

c = F₃(A, B, C, D) = ∑m (0, 1, 3, 4, 5, 6, 7, 8, 9)

d = F₄(A, B, C, D) = ∑m (0, 2, 3, 5, 6, 8)

e = F₅(A, B, C, D) = ∑m (0, 2, 6, 8)

f = F₆(A, B, C, D) = ∑m (0, 4, 5, 6, 8, 9)

g = F₇(A, B, C, D) = ∑m (2, 3, 4, 5, 6, 8, 9)

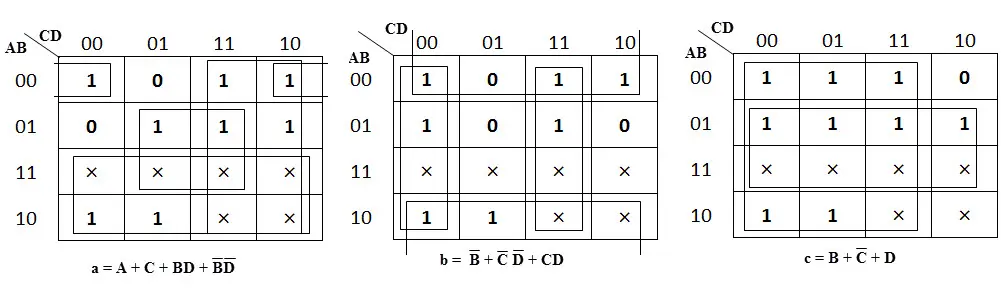

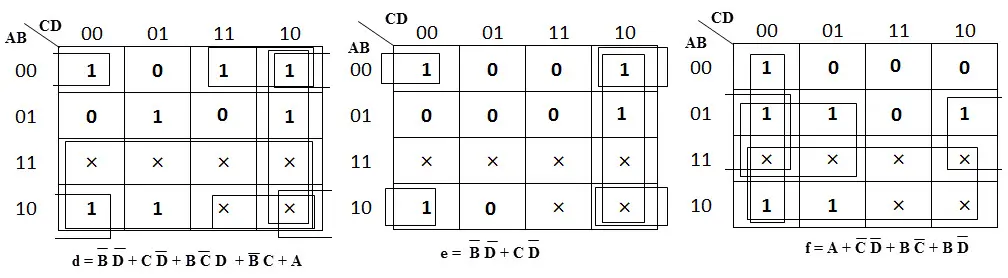

步骤 3: 第三步涉及为每个输出项构建卡诺图,然后对其进行化简,以获得每个输出对应的输入逻辑组合。

3.2 七段显示器卡诺图简化

下图显示为设计组合逻辑电路而简化的共阴七段显示 K 图。

通过以上简化,可得每个输出的逻辑表达式组合。

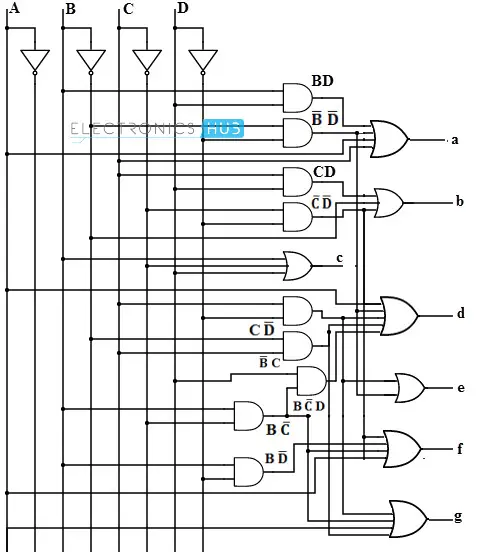

步骤 4:最终构建组合逻辑电路,每个输出信号对应一个逻辑组合。使用 4 个输入(A, B, C, D)和一个七段显示(a, b, c, d, e, f, g)作为输出即可绘出该电路。

4. 显示译码器电路操作

电路的操作可通过真值表理解。当所有输入为低电平时,组合逻辑的输出将驱动除 ‘g’ 之外的所有 LED 导通,从而显示数字“0”。其他输入组合同理,依次对应其他数字显示。

实际中,BCD 到七段译码器以集成电路形式存在,例如 74LS47。除了常规 4 个输入脚和 7 个输出脚,还包含灯测试引脚(用于测试段)、波纹空白输入引脚(在多显示系统中用于消除前导零)、波纹空白输出引脚(用于级联)以及空白输入引脚等功能。

5. 显示译码器电路应用

- 可与定时器和计数器结合,用于显示时钟脉冲数。

- 可改造成字母显示系统,而非仅限十进制数字显示。

- 可用作定时器电路。

6. 显示译码器电路局限性

- 本电路涉及大量逻辑门,结构较为复杂。

- 每个逻辑门会产生延迟,因此用于脉冲计数显示时可能不够准确。

- 该电路为理论电路,可能需要进行一些修改才能实用。