**这是本文档旧的修订版!**

FPGA是一种可编程的数字逻辑芯片,我们可以通过对其编程实现几乎任何的数字功能。可以说在数字世界里它无所不能,就像乐高的积木一样可以搭建各种不同的功能模块,实现你所希望的各种功能,当然,首先你必须掌握最基本的数字逻辑知识,学会一种用来构建各种功能的工具语言(在这里我们推荐广受欢迎的Verilog),再次你要动脑(考验的是你的逻辑思维是否清晰),一个优秀的建筑师的作品是在脑子里勾画出来的,而不是拿积木碰运气拼凑出来的。

用FPGA做设计的一般工作流程:

- 在电脑上通过绘制电路图或者文本文件描述的方式来描述一个你想要实现的“数字功能”

- 在电脑上使用FPGA厂商提供的软件来编译你描述的“逻辑功能”,生成一个可以下载到FPGA内的二进制文件

- 将你的电脑连接FPGA,将上述生成的二进制文件下载到FPGA中去

- 你的FPGA就会执行你设想的“逻辑功能”

记住这些:

- 你可以任意多次地下载配制FPGA,没有次数限制,每次可以是不同的功能。如果在你的设计中出现了错误,只要修复你的”逻辑功能“,再重新编译,再重现下载就可以。不需要重新设计PCB,不需要重新焊接或更换元器件。

- 所有的逻辑都是运行在FPGA内部,也就是硅片上,因此相对于用分立元器件搭建的电路板而言,在FPGA上你的设计会运行的更快

- 每次断电FPGA就会失去其功能,必须在下一次加电的时候重新下载代码才能让FPGA重新工作

都有哪些FPGA厂商?

- Altera是专注于可编程逻辑器件(PLDs)、重配置复杂数字电路的美国公司。该公司于1984年发布器第一款PLD,目前已经是全球最大的PLD供应商,第二大的FPGA供应商,其主要产品线为高端的Stratix,中端Arria以及低端的Cyclone系列FPGA以及MAX系列的CPLDs,其设计软件为Quartus II以及Enpirion 系列的PowerSoC DC-DC电源方案. 2015年12月8日Altera以167亿美元卖给Intel,正式已经成为Intel的一个产品部门 - PSG(可编程系统部)。更多最新信息参见Wikipedia关于Altera的介绍。

- Xilinx是专注于可编程逻辑器件的美国公司,FPGA的发明者也是全球第一个采用Fabless生产模式的半导体公司。Xilinx成立于1984年,总部位于美国加州的San Jose。其主要产品线为高端的Virtex, 中端的Kintex,低端的Artix以及Spartan系列,其设计软件包括Xilinx ISE和Vivado Design Suite, 更多最新信息参见Wikipedia关于Xilinx公司的介绍。

- Lattice Semi是一家高性能可编程逻辑器件(FPGAs,CPLD,一季SPLDs)的美国公司,成立于1983年,在全球有大约700名员工,为全球第三的FPGA供应商,全球第二的CPLDs & SPLDs。其主要产品线为高端的ECP系列,中端的MACH系列以及低端的ICE系列,其设计软件为Lattice Diamond。更多最新信息参见Wikipedia关于Lattice Semiconductor公司的介绍。

- Cypress是美国一家在嵌入式系统领域(汽车电子、工业控制、网络平台到高交互消费、移动设备)专注于高性能、高质量解决方案的设计和生产企业。它提供比较宽泛但差异化的产品线,比如NOR Flash存储器、F-RAM™以及SRAM, Traveo™ 微控制器, 业界独特的PSoC® 可编程片上系统, 模拟和PMIC电源管理集成电路, CapSense® 电容触摸感知控制器,以及无线低功耗蓝牙BLE 和USB连接方案。更多最新信息参见Wikipedia关于Cypress Semiconductor公司的介绍。

- Actel已经被Microsemi收购,主要产品为非易失, 低功耗的FPGA,混合信号FPGA以及可编程逻辑方案。其产品线有反熔丝结构的FPGA和基于Flash的FPGA两种,主要用于高可靠性的领域,比如航空航天。更多最新信息参见Wikipedia关于Actel公司的介绍。

FPGA和CPLD FPGA和CPLD是一回事么?不是的。 Both are programmable digital logic chips and are made by the same companies. But they have different characteristics.

- FPGAs are “fine-grain” devices - that means that they contain a lot (up to 100000) of tiny blocks of logic with flip-flops. CPLDs are “coarse-grain” devices - they contain relatively few (a few 100's max) large blocks of logic with flip-flops.

- FPGAs are RAM based - they need to be “downloaded” (configured) at each power-up. CPLDs are EEPROM based - they are active at power-up (i.e. as long as they've been programmed at least once…).

- FPGAs have special routing resources to implement efficiently arithmetic functions (binary counters, adders, comparators…). CPLDs do not.

In general, FPGAs can contain large digital designs, while CPLDs can contain small designs only.

FPGA和微控制器: Are FPGAs and microcontrollers the same thing? No

- FPGAs implement programmable logic elements running in a parallel fashion.

- Microcontrollers are based on a CPU architecture (executes a set of instructions in a sequential manner).

Microcontrollers have on-chip peripherals that also execute in parallel with their CPU. But they are still much less configurable than FPGAs.

在进入正式的学习之前,先给大家提供两本基础的英文书,同学们可以下载了进行阅读(在无法上网和流量将用尽的时候最好、最让自己不内疚的消遣方式)

- 傻瓜都能掌握的FPGA知识: FPGA for Dummies

- 美国大学的数字电路/Verilog教程(基于Digilent的板卡,使用的是Xilinx的芯片)Introduction to Digital Design Using Digilent FPGA Boards

同时建议大家能够大量阅读维基百科上面关于FPGA的词条信息,访问维基百科不需要翻墙,但同学们一定要阅读英文的资料,而不是中文的。

来,正式开始宏大的FPGA学习历程。。。

1 数字逻辑、可编程逻辑及FPGA

FPGA(Field Programmable Gate Array)译作中文为:现场可编程门阵列,也就是设计者可以在现场对可定制的数字逻辑进行编程的集成电路,相比于其它的硬件构成,它允许你构建你所需要的硬件而不需要ASIC(专用集成电路),而且比采用微处理器内核更简单、快速、省电。

关于FPGA的大概介绍,参考我们的培训文档:ECBC可编程逻辑基础PPT

1.1 为什么用FPGA?

FPGA的技术优势:灵活的开发周期、更低的设计迭代成本、更低的一次性工程费用(NRE),易于评估和实现的可选设计架构,新产品上市时间快。 相比于ASIC和MCU来讲,FPGA具有以下优势:

- 开发快,上市时间短,适合原型设计或小批量产品,FPGA高度灵活,设计实现和后续优化的灵活性可以显著影响项目的进度、设计的复杂度,降低项目的风险,便于更改和升级。

- 重复编程/配置,灵活、快速

- 集成度高,可以通过选用不同规模的器件实现自己所需要的功能,内部功能模块之间的通信和接口的速度、性能都会较多个分立的芯片之间互连有明显的改善,节省板卡空间,便于调试

1.2 FPGA设计需要的技能

FPGA在各个领域都是必不可少的一种硬件工具,掌握并有效使用FPGA对当代的电子设计工程师来讲是非常必要的,要做到较好的FPGA设计需要具备如下的一些技能:

1.2.1 具备自己设计高速数字电路板(PCB)的能力并且掌握[[DSP]]的基础理论

- PCB硬件与接口设计

- 逻辑电路设计

- 硬件仿真

- 硬件模块调试

- PCB设计布局

- 信号完整性及终端匹配

- DSP算法的硬件实现

- 功耗与去藕设计

- 板级引脚分配

- I/O特性的定义

- 设计优化权衡

- FPGA器件和封装选择

1.2.2 还要掌握至少一门硬件描述语言(HDL)

- HDL语言的设计输入

- 测试平台的开发

- 设计约束

- 脚本实现自动化处理

- HDL流程文件的配置管理

- 支持设计复用

1.2.3 从系统高度设计你的系统

- 处理器需求分析

- 处理器架构选择

- 系统级设计的层次结构定义

- 系统模块的集成与接口测试

- 数据流的定义

- 硬件/软件实现的权衡

- 功能划分和模块化设计

- 系统级测试、调试和验证

1.2.4 具体实现 - 通过软件/DSP设计

- 处理器代码模块的定义

- DSP算法的软件实现

- 在处理器上运行操作系统

- 代码的编写和测试

- 常规的代码调试和验证

- 代码的配置管理

1.3 PLD/FPGA的结构

1.3.1 FPGA基本功能

1.3.2 FPGA增强功能

- 内置处理器:软核 & 硬核 & DSP

- IO:多种高速收发、DDR存储器访问、可编程数控阻抗

- 嵌入MAC单元 - 高效浮点运算

- 系统监控:内置ADCs

1.5 FPGA的选型决策原则

- 功能/资源:逻辑单元、存储器、处理能力、IO、处理器内核、DSP

- 封装:满足管脚数量以及板卡的物理尺寸要求

- 功耗:满足系统对供电的限制需求

- 开发工具/难度:影响设计难度和开发时间,尽可能选择易于开发、调试的器件架构

- 系统成本:包括配置RAM、外供电源、时钟等,除了器件成本之外还要考虑实现成本、支持成本等。

- 购买难度:价钱/数量/供货渠道

- 灵活性:便于将来的产品修改和升级

- 技术支持:供应商是否能够提供良好的技术支持,乃至培训

1.6 设计流程及工具

当前FPGA的设计最常用的都是通过硬件描述语言(HDL),主要有两种 - Verilog HDL或VHDL语言。

1.7 FPGA应用中的注意事项

1.7.1 硬件设计

- 管脚分配:输入/输出类型,预留功能管脚,方便布线

- 电源:内核电压/接口电压及其相应电流,上电时序

- 编程:JTAG、配置、在线更新

- 测试点:关键信号 - 时钟、电源、关键IO

1.7.2 代码开发

- 善用IP Core:调用原厂提供的经过验证过的IP内核

- 硬件设计概念:并行工作、时延

- 充分仿真:功能仿真、时序仿真、TestBench

- 调试:使用原厂提供的片上逻辑分析工具

1.8 FPGA学习和使用要借助的资源

- 工具:开发板、评估板、调试工具、编译/仿真软件

- IP Cores:原厂/官方提供、开源组织、其他人验证

- 参考设计: 设计指南、系统应用、视频教程

- 技术支持:原厂的FAE、第三方设计公司、社区/论坛/QQ群

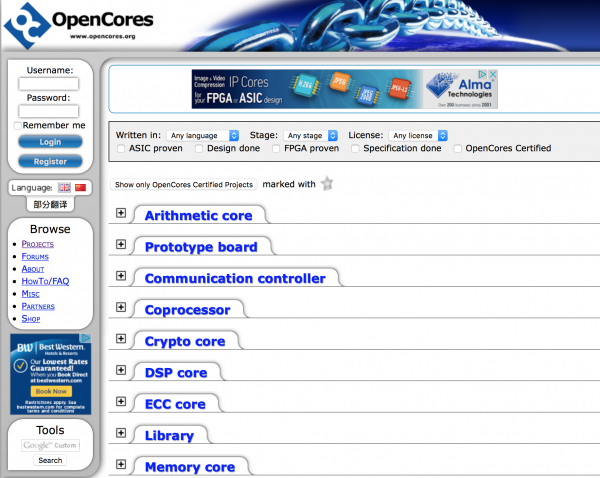

1.9 IP Cores的有效使用

随着电子系统越来越复杂,我们不可能任何一个设计都从头自己写代码,必须学会站在巨人的肩上,充分利用现有的资源,尽快地完成自己的设计。经过几十年可编程逻辑技术的发展,可以说几乎所有的常见功能都能够找到可以参考甚至可以直接调用的IP内核,获取这些IP、能够争取地使用这些IP就是一种非常重要的能力。到哪里去找到可靠使用的内核呢?推荐如下几个途径:

随着电子系统越来越复杂,我们不可能任何一个设计都从头自己写代码,必须学会站在巨人的肩上,充分利用现有的资源,尽快地完成自己的设计。经过几十年可编程逻辑技术的发展,可以说几乎所有的常见功能都能够找到可以参考甚至可以直接调用的IP内核,获取这些IP、能够争取地使用这些IP就是一种非常重要的能力。到哪里去找到可靠使用的内核呢?推荐如下几个途径:

- 来自原厂的IP内核:一般已经包含在其编译系统中,其官方网站上也会有很详细的文档介绍,关于该IP内核的功能、结构调用、所支持的器件、所占的系统资源等。

- 国际知名开源网站上的IP核:比如www.opencores.org,这个网站几乎在全球的FPGA开发者中间家喻户晓,几乎任何重要的逻辑功能模块都能够在这个网站上找到相应的参考。那些经过WBC认证的代码质量会比较高,不过由于每个人的设计场景会稍微不同,直接调用这些IP Cores未必合适,能够参考这些IP核的设计思路也是对自己的设计非常有益的。

- 我们StepFPGA将来也会围绕我们的小脚丫FPGA平台将用户构建的各种优秀功能模块经验证、审核以后发布出来,也希望通过这么一个开源的平台帮助大家的学习和设计。也希望更多的设计者能够将自己的设计贡献、分享出来。

2 Lattice Semiconductor的MachXO2系列FPGA

在我们的学习系统中我们选用了Lattice Semiconductor公司的MachXO2系列FPGA,主要出于以下几方面的考虑:

在我们的学习系统中我们选用了Lattice Semiconductor公司的MachXO2系列FPGA,主要出于以下几方面的考虑:

- Lattice Semiconductor公司的FPGA学习和使用门槛最低,易学易用

- 性价比高,除了适合入门级的学习之用,还能够满足80%以上的企业应用

- 非常适合于高校教学实验及创新实践

本节我们来看看我们选用的这个系列的FPGA有哪些特点以及应用领域。

2.1 特性

- 灵活的逻辑架构,256-6864个查找表(LUTs),18-334个输入输出管脚(PIOs)

- 超低功耗 - 采用先进的65nm低功耗工艺,等待状态时功耗低至22μW,具有可编程、低摆动的差分I/O

- 最高达334个hot-socketable输入/输出管脚避免额外的泄漏

- TransFR特性允许在现场设计更新而不干扰设备的运行

- 灵活的片上时钟处理 - 8个主时钟输入管脚、支持高速I/O的双沿时钟、每个器件内有2个模拟PLL、外部时钟输入时频率范围从7MHz到400MHz

- 芯片内有5.5%精度的片上振荡器

- 每颗芯片都有TraceID进行追踪

- 最小封装为2.5mmx2.5mm

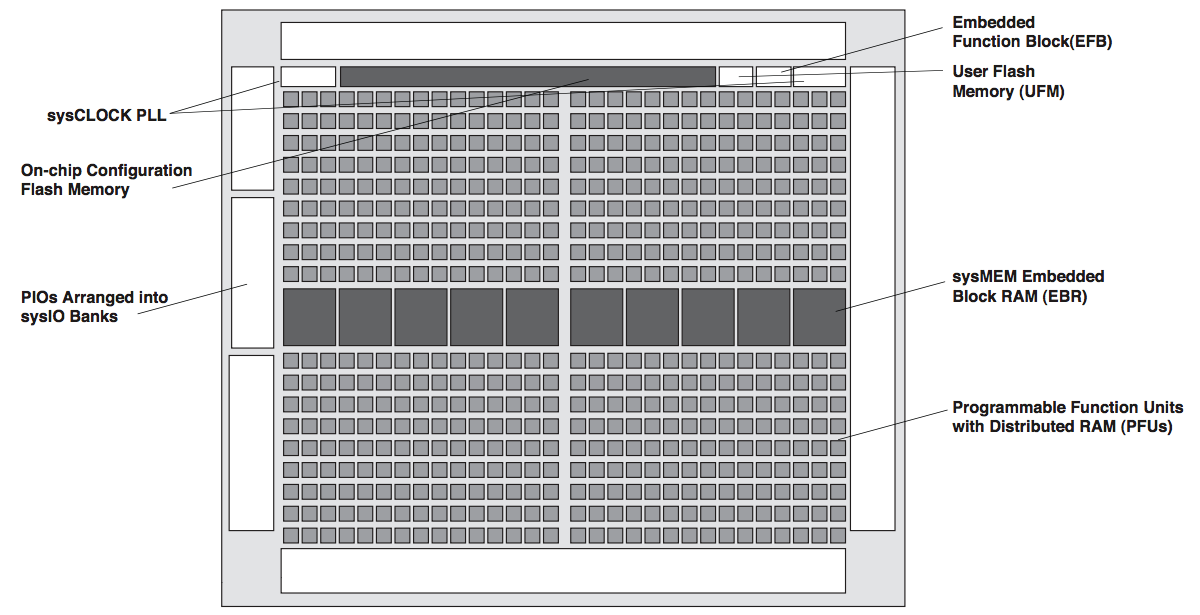

2.2 结构

MachXO2内部结构功能

可编程部分:

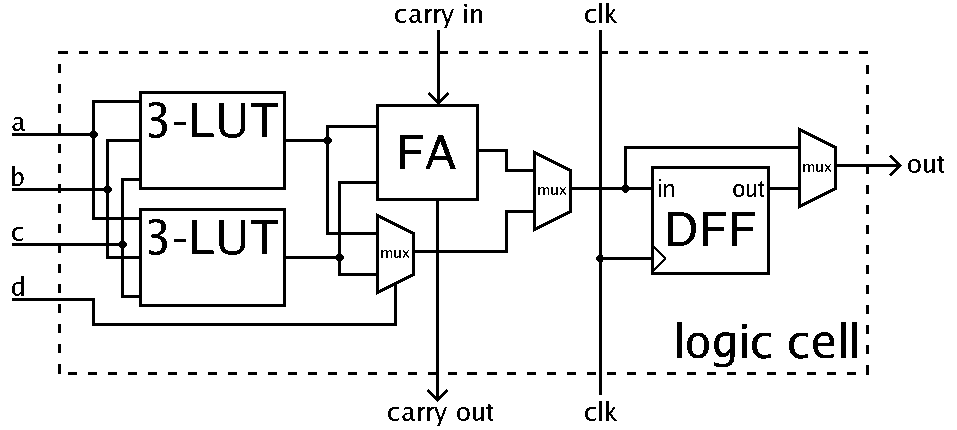

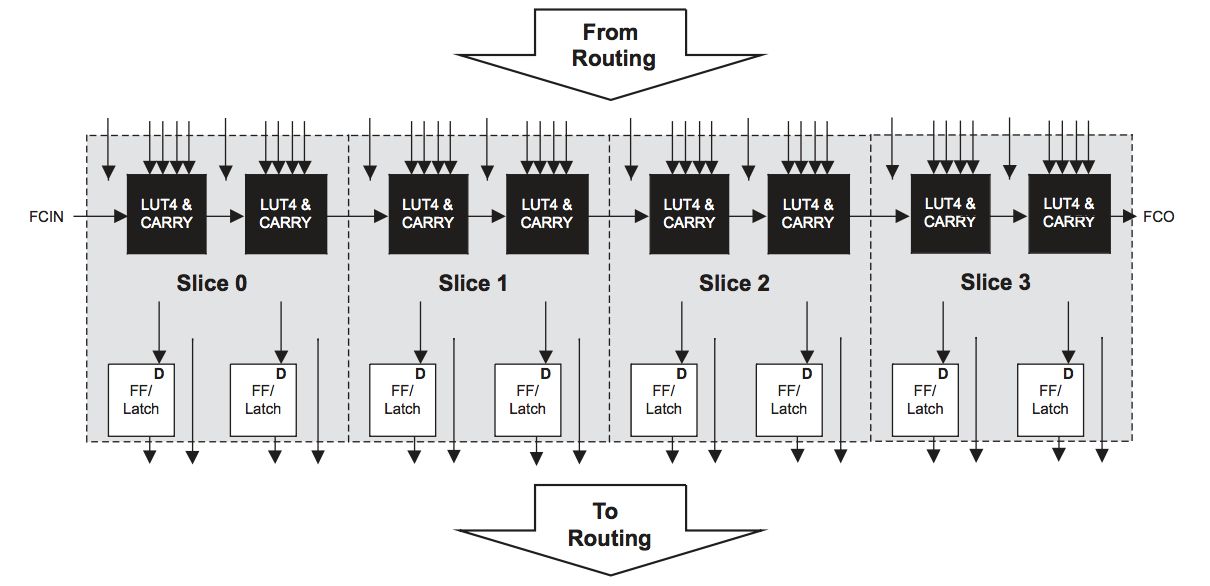

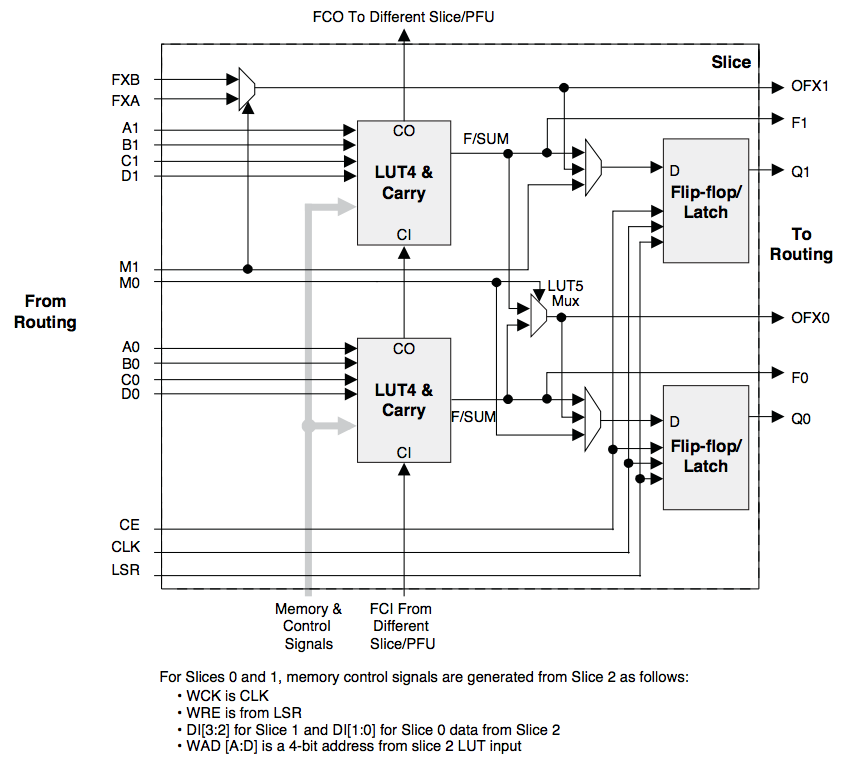

- FPGA的核心部分是由逻辑门(Logic Gate)、寄存器(Register)以及连线(Wire)构成的可编程的逻辑块,也即此图中的PFUs(Programmable Function Units with Distributed RAM - 带分布式存储器的可编程功能单元),这些逻辑块的规模由两个重要指标表示LUTs和Slices

- 可编程输入输出管脚PIOs:分成多个Bank的sysIO,每个Bank可以有单独的供电电压Vccio,以支持不同电平的数据传输协议,这些输入输出管脚可以自由分配,并可以通过编程、配置支持多种数据传输协议(不同电平、差分等),IO管脚的输入输出电阻也可以编程、配置

- 块RAM:在这里称为sysMEM Embedded Block RAM(EBR)

硬核部分: 当今的FPGA除了可编程的逻辑和IO之外,还提供了一系列常用的功能模块,以硬核的方式内嵌在芯片以内,即便用户在设计中不用这些功能,这些资源也存在于系统中。硬核化的优势在于速度快、功耗低,且这些硬核一般为常用的功能块。在MachXO2中内嵌的硬核功能主要有:

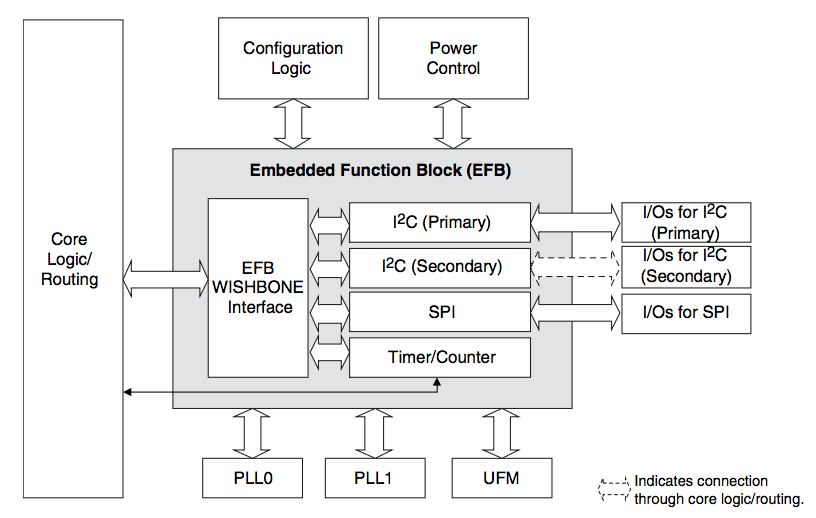

- 嵌入式功能块:Embedded Function Blocks(EFB)- MachXO2主要的EFB包括一个SPI、两个I2C、和一个定时器

- 程序Flash:On-chip Configuration Flash Memory

- 用户Flash:User Flash Memory(UFM)

- PLL/DLL: sysPLL

MachXO2内部的可编程功能单元构成示意图

MachXO2的Slice构成示意图

MachXO2内部的嵌入式功能模块

2.3 资源

上面我们介绍了MachXO2内部的结构,XO2系列不同的型号内部结构是相同的,但资源的多少则取决于所选择的型号,在设计中我们需要根据资源的需求来选用合适的器件,了解到这些器件的资源配置对于我们设计也是有帮助的,可以充分利用器件内部的资源简化外围电路的设计,同时也要知道器件内部的局限性,在外围进行扩展。在我们小脚丫2.0版本中我们选用了XO2-4000的型号(参见MachXO2选型表),它具有如下资源:

- 4320个查找表

- 10个嵌入式RAM块,攻击92kbits的容量

- 34kbits的分布式SRAM

- 96Kbits的用户Flash存储器

- 支持DDR/DDR2/LPDDR存储器接口

- 内部具有配置用的Flash

- 支持双启动模式

MachXO2 选型表

| O2-256 | XO2-640 | XO2-640U | XO2-1200 | XO2-1200U | XO2-2000 | XO2-2000U | XO2-4000 | XO2-7000 | |

| 查找表(LUTs)的密度 | 256 | 640 | 640 | 1280 | 1280 | 2112 | 2112 | 4320 | 6864 |

| EBR RAM块(9 Kbits/block) | 0 | 2 | 7 | 7 | 8 | 8 | 10 | 10 | 26 |

| EBR SRAM(Kbits) | 0 | 18 | 64 | 64 | 74 | 74 | 92 | 92 | 240 |

| Dist. SRAM (Kbits) | 2 | 5 | 5 | 10 | 10 | 16 | 16 | 34 | 54 |

| 用户Flash存储(Kbits) | 0 | 24 | 64 | 64 | 80 | 80 | 96 | 96 | 256 |

| PLL + DLL | 0 | 0 | 1 + 2 | 1 + 2 | 1 + 2 | 1 + 2 | 2 + 2 | 2 + 2 | 2 + 2 |

| 支持DDR/DDR2/LPDDR存储器 | - | - | Yes | Yes | Yes | Yes | Yes | Yes | Yes |

| 配置存储器 | 内部Flash | ||||||||

| 双启动 | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes |

| 内嵌功能块 | I2C (2), SPI (1), Timer (1) | ||||||||

| 内核电压Vcc 1.2 V | ZE | ZE | - | ZE | - | ZE & HE | HE | ZE & HE | ZE & HE |

| 内核电压Vcc 2.5 - 3.3 V | HC | HC | HC | HC | HC | HC | HC | HC | HC |

2.4 管脚分配

2.5 主要应用领域

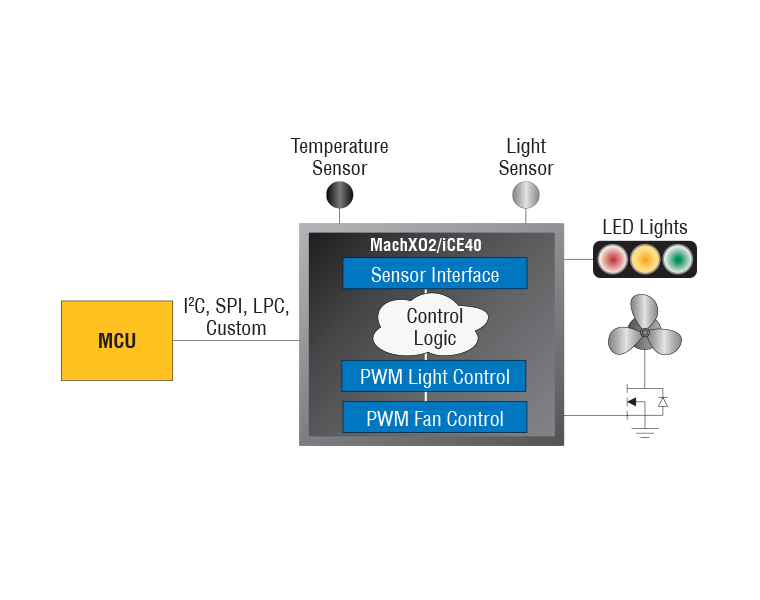

2.5.1 微处理器的接口扩展

2.5.2 提高实时性要求较高的功能的性能

- 在系统上电时通过快速启动逻辑精确地控制信号

- 可以配置PWM功能以精确产生照明和马达控制所需要的模拟电压

- 构建传感器缓冲器以及智能中断以保证实时世界的事件能够被捕捉

- 采用硬件UART克服采用软件实现UART的性能限制

2.5.3 通过硬件加速提高系统的性能

2.6 相关设计文档

3 开发工具

3.1 Lattice Diamond集成化开发环境

- Diamond安装及配置,包括软件的下载、License的申请以及软件的安装整个过程。

- Lattice Diamond的使用,以最简单的点亮LED灯为例,简单介绍了一下该软件从编辑输入开始到最终的bitstream下载到FPGA。

3.2 硬件描述语言

在设计FPGA逻辑中有两种硬件设计语言(HDL)可以选择,一种是Verilog HDL,还有一种是VHDL,在我们的设计中选用普及率更广,更容易上手的Verilog,具体如何使用,可以参考如下的几个PPT教程: