**这是本文档旧的修订版!**

Quartus Prime的上手使用

1.创建第一个工程

1.1新建工程

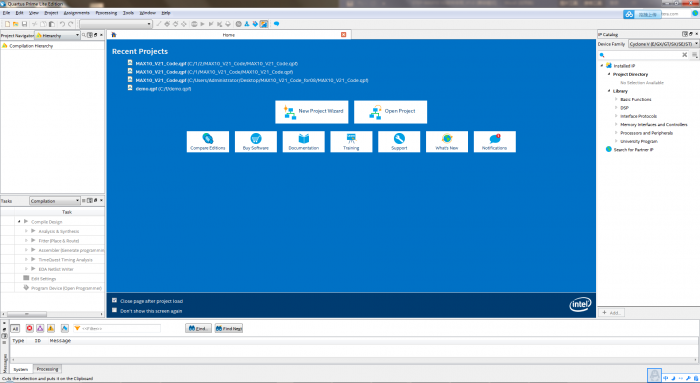

(1)启动Quartus软件:双击Quartus系列软件图标,界面如下(以Quartus Prime16.1为例)。

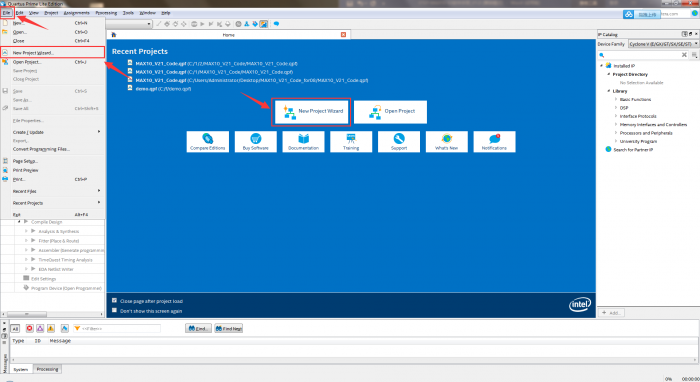

(2)创建工程:点击File→New Project Wizard选项 或 点击Home页面中的New Project Wizard图标。

(2)创建工程:点击File→New Project Wizard选项 或 点击Home页面中的New Project Wizard图标。

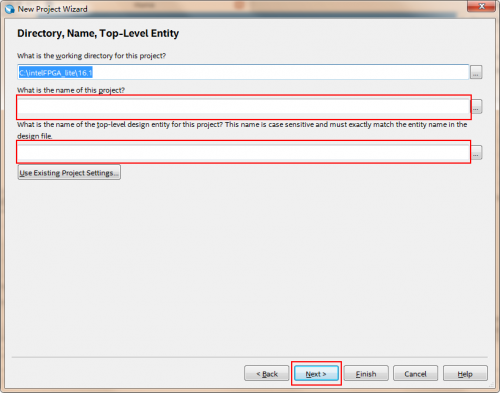

(3)工程目录、名称填写:(注意:工程目录中不能有汉语、空格等字符)

(3)工程目录、名称填写:(注意:工程目录中不能有汉语、空格等字符)

- 工程目录:选择新建工程的目录;

- 工程名称:填写工程名称;

- 顶层模块名称:设计文件中top module的模块名称,软件默认跟工程名称相同。

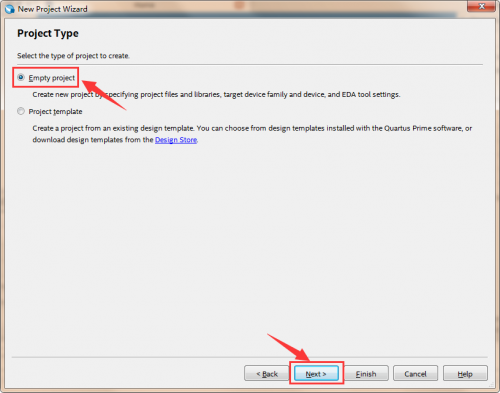

(4)工程类型:选择Empty project,点击Next。

(4)工程类型:选择Empty project,点击Next。

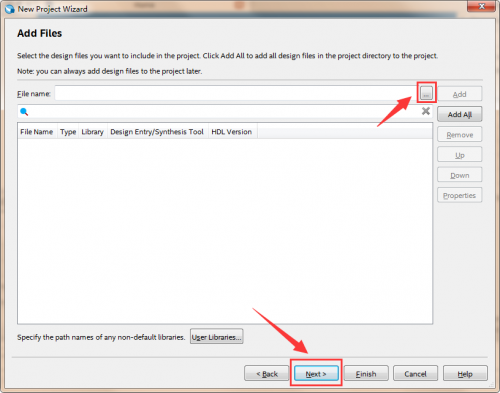

(5)添加文件,如果已有设计文件,在当前页面选择并添加,点击Next。

(5)添加文件,如果已有设计文件,在当前页面选择并添加,点击Next。

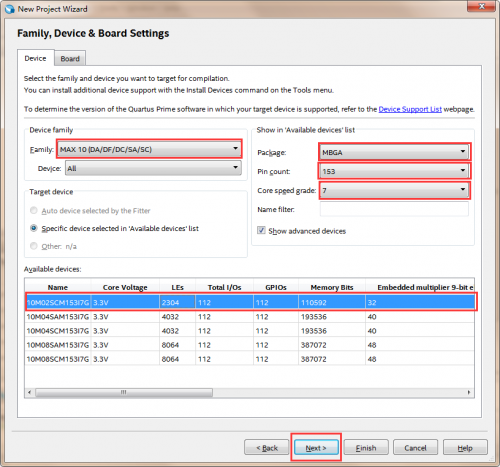

(6)器件选择:根据开发平台使用的FPGA选择对应器件(10M02SCM153I7G/10M08SCM153C8G),点击Next。

(6)器件选择:根据开发平台使用的FPGA选择对应器件(10M02SCM153I7G/10M08SCM153C8G),点击Next。

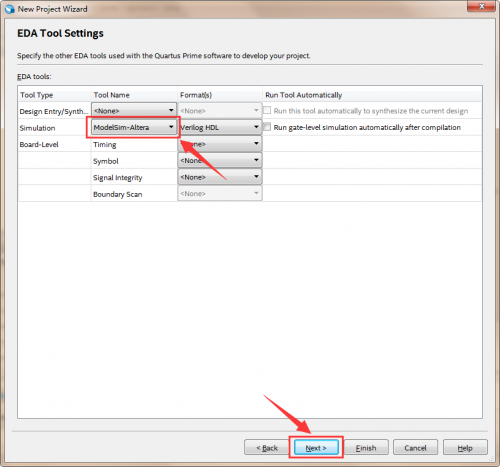

(7)EDA工具选择:选择第三方EDA工具:如果有需要可以选择第三方的综合或仿真工具(第三方工具需要另外安装并设置启动路径),这里我们选择使用modelsim工具仿真,点击Next。

(7)EDA工具选择:选择第三方EDA工具:如果有需要可以选择第三方的综合或仿真工具(第三方工具需要另外安装并设置启动路径),这里我们选择使用modelsim工具仿真,点击Next。

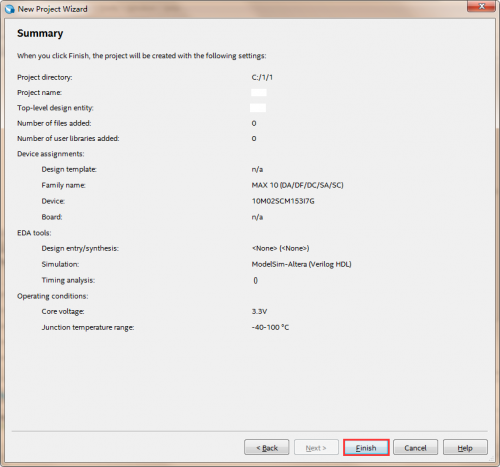

(8)工程设置确认:确认工程相应的设置,如需调整点击Back返回修改,若确认设置,点击Finish。

(8)工程设置确认:确认工程相应的设置,如需调整点击Back返回修改,若确认设置,点击Finish。

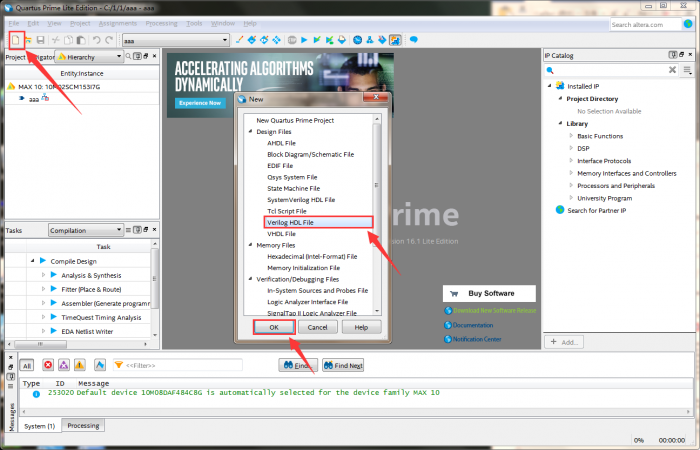

(9)工程创建完毕,Quartus软件自动进入开发界面,如下:

(9)工程创建完毕,Quartus软件自动进入开发界面,如下:

1.2添加设计文件

(1)选择File→New 或 点击工具栏中的New按钮,选择Verilog HDL File文件类型,点击OK,Quartus软件会新建并打开Verilog文件。

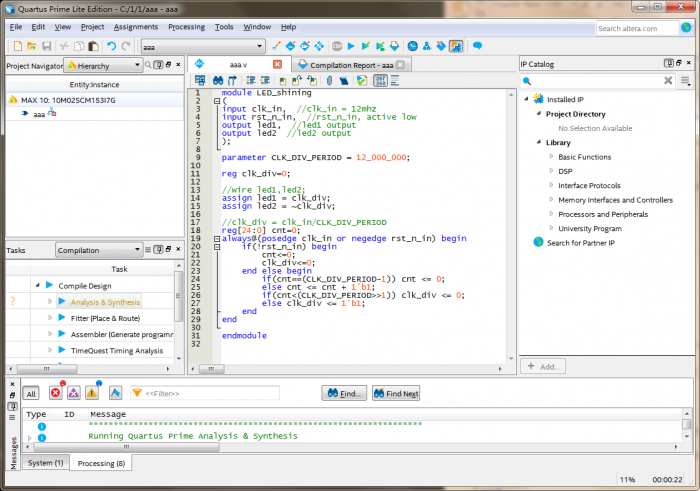

(2)在新建的Verilog文件中进行Verilog HDL代码编写、保存,文件名为LED_shining.v,如下图所示,程序源码如下。

(2)在新建的Verilog文件中进行Verilog HDL代码编写、保存,文件名为LED_shining.v,如下图所示,程序源码如下。

程序源码

程序源码

// ******************************************************************** // >>>>>>>>>>>>>>>>>>>>>>>>> COPYRIGHT NOTICE <<<<<<<<<<<<<<<<<<<<<<<<< // ******************************************************************** // File name : LED_shining.v // Module name : LED_shining // Author : STEP // Description : LED_shining // Web : www.stepfpga.com // // -------------------------------------------------------------------- // Code Revision History : // -------------------------------------------------------------------- // Version: |Mod. Date: |Changes Made: // V1.0 |2017/03/02 |Initial ver // -------------------------------------------------------------------- // Module Function:闪烁LED module LED_shining ( input clk_in, //clk_in = 12mhz input rst_n_in, //rst_n_in, active low output led1, //led1 output output led2 //led2 output ); parameter CLK_DIV_PERIOD = 12_000_000; reg clk_div=0; //wire led1,led2; assign led1 = clk_div; assign led2 = ~clk_div; //clk_div = clk_in/CLK_DIV_PERIOD reg[24:0] cnt=0; always@(posedge clk_in or negedge rst_n_in) begin if(!rst_n_in) begin cnt<=0; clk_div<=0; end else begin if(cnt==(CLK_DIV_PERIOD-1)) cnt <= 0; else cnt <= cnt + 1'b1; if(cnt<(CLK_DIV_PERIOD>>1)) clk_div <= 0; else clk_div <= 1'b1; end end endmodule

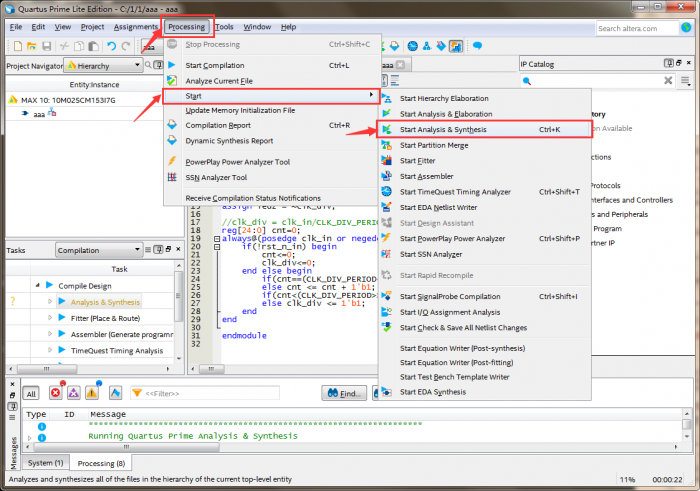

(3)选择菜单栏中Processing→Start→Start Analysis & Synthesis选项 或 工具栏中Start Analysis & Synthesis按钮,如下图所示。

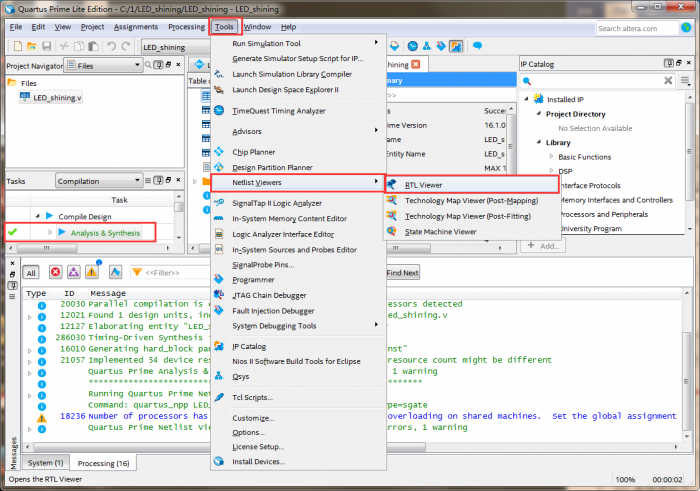

(4)Quartus软件会完成分析综合,若设计没有问题,综合Tasks栏中Analysis & Synthesis会变成绿色,同时左侧出现绿色对勾。可以选择Tools→Netlist Viewers→RTL Viewer查看电路。

(4)Quartus软件会完成分析综合,若设计没有问题,综合Tasks栏中Analysis & Synthesis会变成绿色,同时左侧出现绿色对勾。可以选择Tools→Netlist Viewers→RTL Viewer查看电路。