100Msps单通道/单电源示波器及频率计

数据采集卡的物理尺寸及基本功能

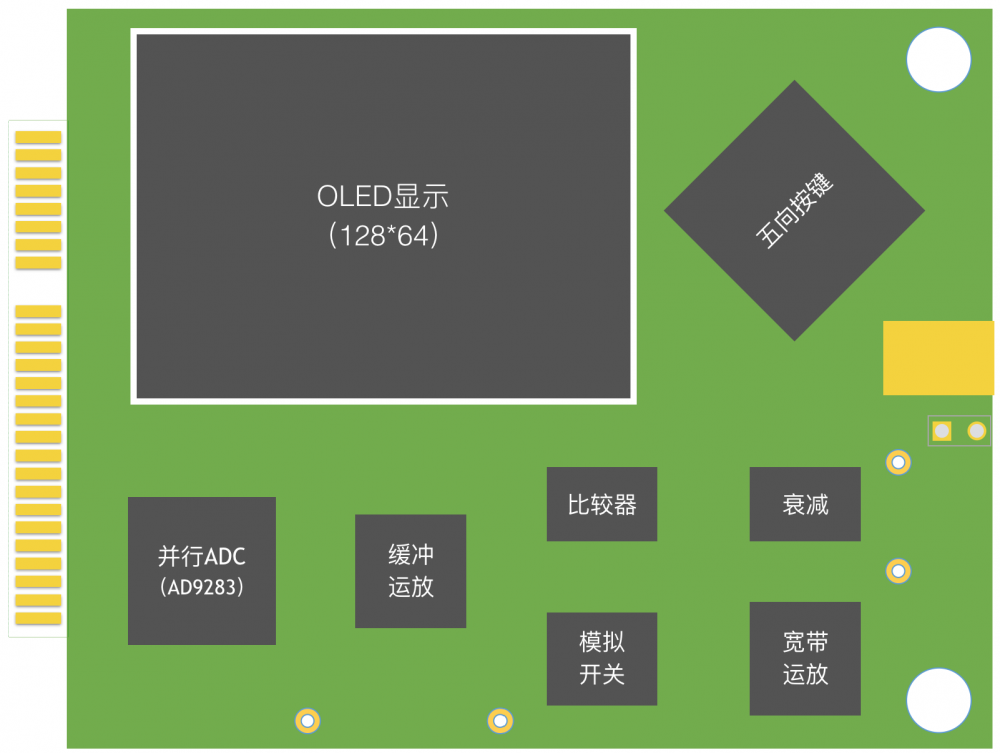

1.具有产生正弦波、方波、三角波三种周期性波形的性能。 2.输入信号幅值为几毫伏到10v左右,带宽为30M,采样率为100bmps。 3.输出信号幅度为0-3.3v 5频率测量 4.oled实时显示采样波形 6.外部按键调节水平扫描时间和垂直灵敏度

功能需求

器件选择

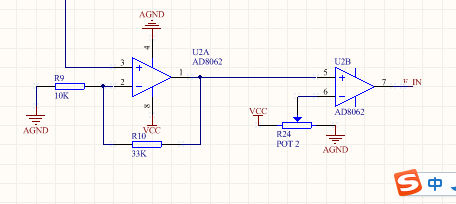

1.根据3.3v单电源供电方案,宽带运放选择AD80632双运放,带宽达300M,轨至轨输出,低噪声。 2.ADC芯片:我们采用分辨率为8位,采样率达80-100MSPS的高速转换芯片ADC9283,根据乃奎斯特定理,能够保证采集的点能够复现出波形。 3.模拟开关:选择四路模拟开关,分别控制4路前级运放的增益信号,已保证ADC能够输入的信号幅度为1vpp。 4.OLED:选择分辨率为128*64d的0.96寸OLED,采用4线SPI与FPGA通信。

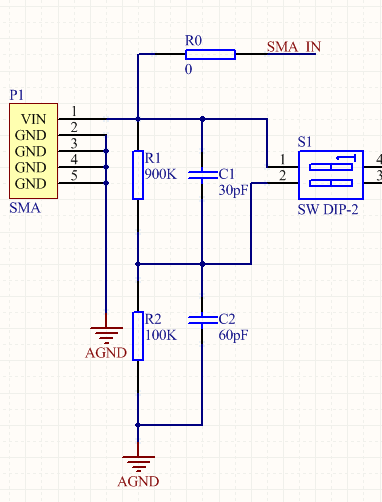

原理图说明

1.输入信号采用SMA射频头传输,采用无源电阻分压对大信号进行10倍衰减,小信号不衰减,并联电容进行高频补偿,2路开关选择是否衰减。 2.考虑到电路输入阻抗较大,故采用射极跟随器与后极放大电路缓冲。 3.通过四路模拟开关对衰减的信号进行x10.x5.x2 x1进行相应的比例放大,以满足ADC采样电路的输入为1vpp。 4.8位高速ADC对模拟信号进行数字量化,通过FPGA对数据进行相应的处理以驱动OLED显示波形。 5.OLED采用4线SPI与FPGA通信。

{{:b.png?nolink|}} {{:cccc.png?nolink|}}

{{:eeee.png?nolink|}}

PCB布局布线

.PCB部分设计:根据板框和装配要求,器件按信号流行模块化布局,规则设置要满足厂家生产工艺要求及电气规则,高速器件走线进行阻抗匹配,模数地分割,丝印不盖住过孔和元器件外形轮廓等等

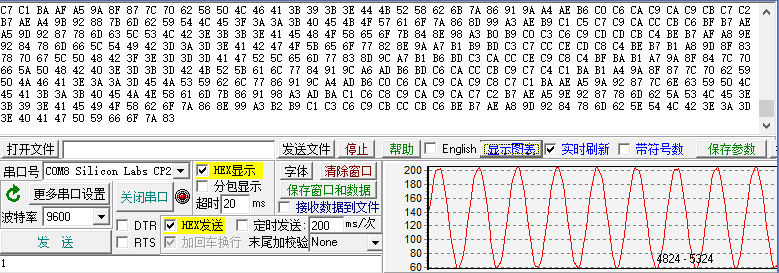

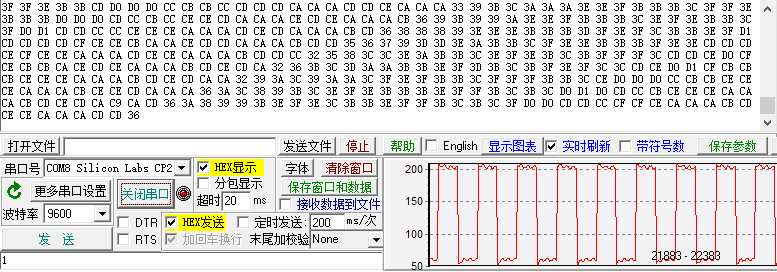

板卡调试

功能调试: 1.用万用表检测电源和地是否短路 2.上电时电流是否过大,否则可能有短路现象 3.根据电路原理设计分级调试,输入信号源以及示波器观测信号幅值,频率,失真度,增益等等。 4.通过串口发送数据驱动OLED,保证显示屏驱动电路是否正常工作。 问题和解决方法:SMA射频头信号有所失真,通过调节补偿电容改善。

FPGA逻辑实现

1.在顶层我们设计的模块有adc9283、FIFODC、Baud、sendctrl、UartTx、Generater100mbps(ramforoled、oledbyram),顶层模块名uartmy3 uartmy3模块和Generater100mbps是同时设计的,验证过后将两个模块连接在一起实验功能。之所以使用串口模块是因为方便调试,将FIFO输出的数据通过串口发送到PC端,用串口调试助手观察波形。 adc9283:给AD9283提供时钟输入 FIFODC:使用4K的FIFO缓存AD转换后的数字量数据 Baud:波特率发生模块 sendctrl:波特率选择模块 UartTx:串口数据发送 ramforoled:128×64的RAM IP核模块,用于存放FIFO发送的数据 oledbyram:通过SPI将数据发送到OLED上进行显示、控制OLED刷新和屏幕的驱动 2.关键模块实现 比较关键的代码主要有AD9283串行输入数据转换成8位并行数据输出、FIFO数据的缓存、双口RAM模块、屏幕驱动模块。 8位并行数据输入:根据AD9283的时钟以此读取输入的模拟信号,输入AD9283的时钟是12Mhz系统时钟进行8分频后进行模拟数据的采集,将采集后的数据输出给FIFO。 FIFO数据的缓存:使用Dimond中的IP核,容量为4KB,输入数据为AD9283的输出数据,输出数据送入RAM中,写入FIFO数据的时钟和AD9283的时钟是同步的。 双口RAM模块:使用Dimond中的IP核,容量为128×64,输入数据为FIFO的输出数据,输出数据送入屏幕驱动模块,系统时钟的300分频作为串口的波特率、RAM的数据写时钟和FIFO的读时钟。 屏幕驱动模块:将RAM中读出的数据通过OLED驱动模块显示到屏幕上。

3.关键知识点、难点

整个代码中比较复杂的就是OLED屏幕驱动控制部分的数字逻辑的代码比较难实现

测试报告及说明