**这是本文档旧的修订版!**

38译码器

====硬件平台====

====设计要求====

- 掌握38译码器的基本原理

- 掌握组合逻辑的设计

- 掌握case的基本语法

- 使用拨码开关实现译码器输入功能

- 基于小脚丫STEP FPGA Base Board开发平台拨码开关输入,LED输出实现38译码器功能

====工作原理====

===38译码器原理===

译码器的逻辑功能是将每个输入的二进制代码译成对应的输出高、低电平信号或另外一个代码。

38译码器由三路信号输入,八路信号输出的译码器(2^3 = 8)。

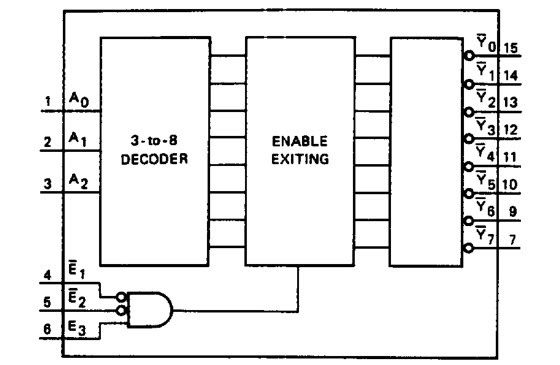

以芯片74HC138为例:

由上图芯片使能由E1,E2,E3共同控制

三路信号输入:A0,A1,A2

八路信号输出:Y0,Y1,Y2,Y3,Y4,Y5,Y6,Y7

====硬件连接====

结合74HC138的结构原理及实验平台STEP-Baseboard的硬件配置,我们使用:

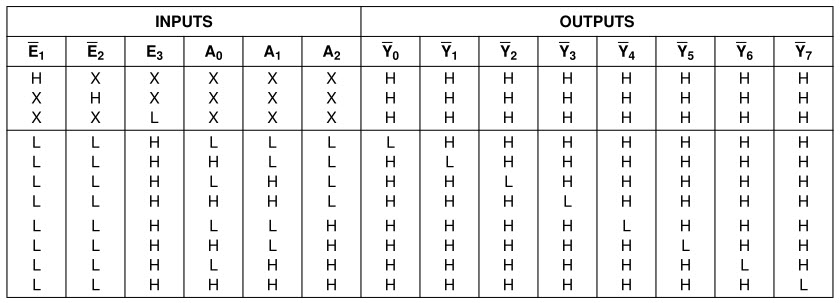

- 一个拨码开关(S5)替代E1、E2和E3的逻辑运算结果,作为芯片使能管脚

- 三个拨码开关(S1、S2、S3)作为38译码器的三路信号输入管脚

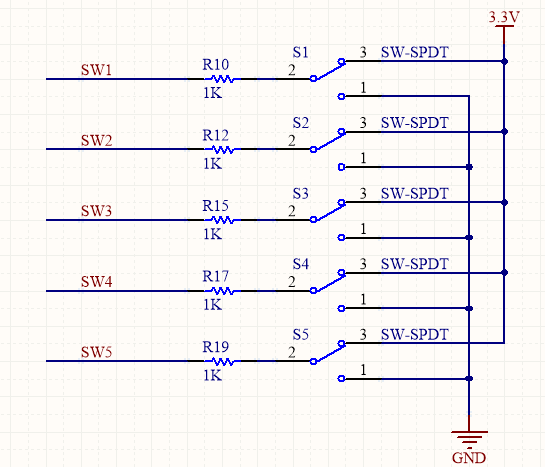

- 八个LED灯作为38译码器的八路信号输出管脚

====代码设计====

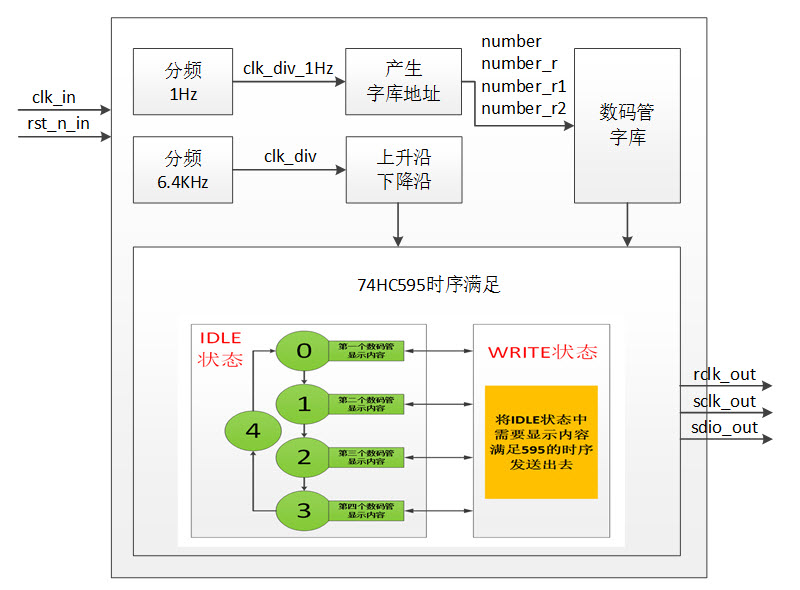

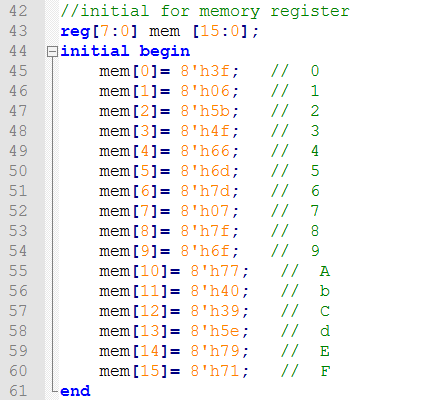

数码管是针对数字的显示器件,显示内容相对固定,我们首先把需要显示的内容定义为存储器,这样当我们需要显示时,只需要有存储器的地址就可以调用数据。

我们的数码管是由芯片74HC595驱动的,根据上面计算,SHCP的频率为6.4KHz,所以我们首先分频产生一个6.4KHz左右的信号clkdiv,然后再基于这个信号产生74HC595的控制时序。

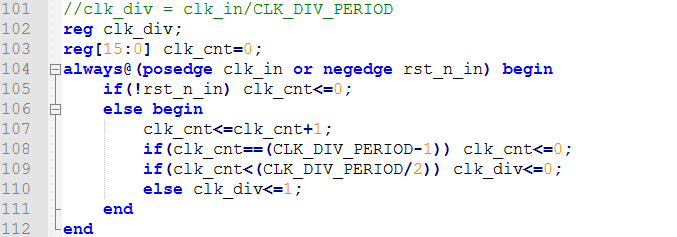

小脚丫开发板晶振为25MHz,我们需要对时钟分频得到6.4KHz左右的信号,这样分频系数为25MHz/6.4KHz ≈ 3900。

parameter CLKDIVPERIOD=3900;

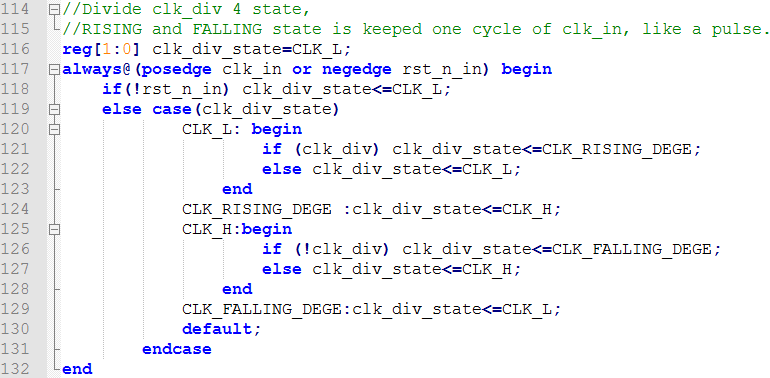

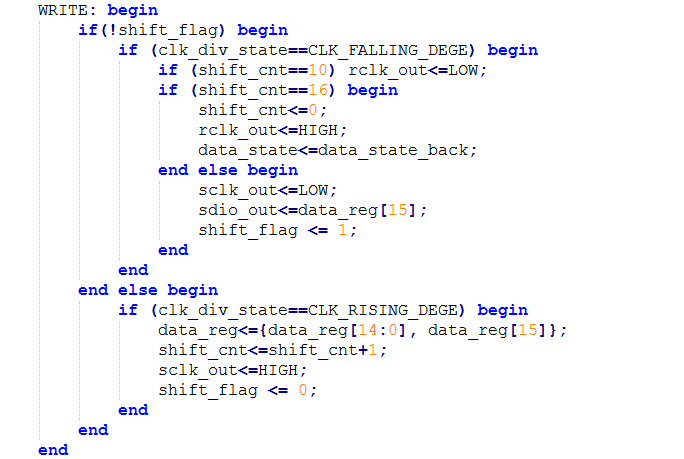

然后我们使用状态机将clk_div的高电平、低电平、上升沿和下降沿产生脉冲,方便我们后面结合上升沿和下降沿的状态完成74HC595的控制时序。

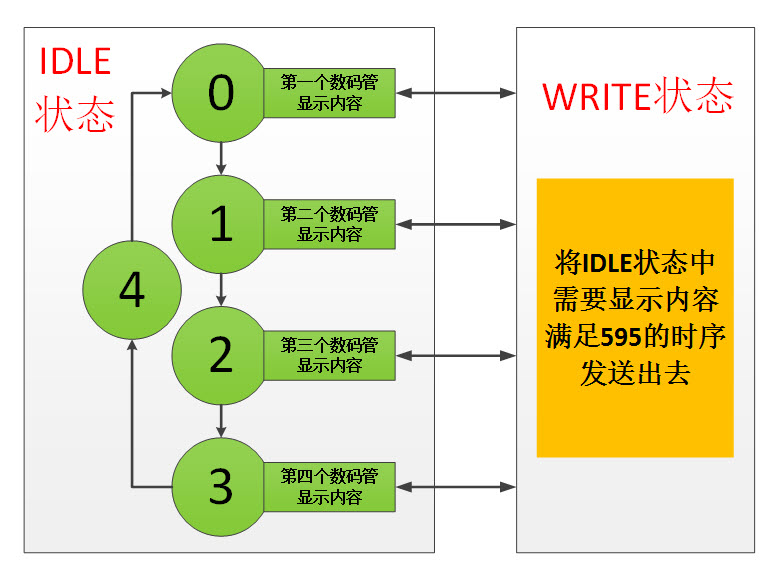

使用状态机我们将赋值和并行转串行分别完成,分为两个状态:

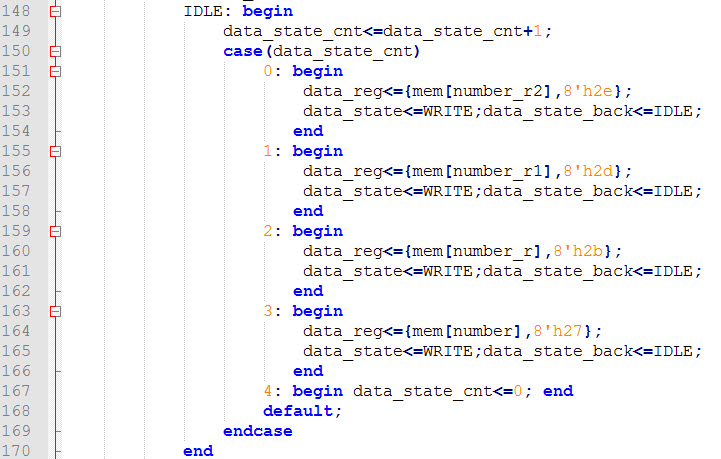

- IDLE状态:分时控制四位数码管各位需要显示的内容

- WRITE状态:实现74HC595的控制时序,将数码管需要显示的内容发送出去

- IDLE状态:分时显示的程序设计如下:

- WRITE状态:实现74HC595的控制时序,串行输出的程序设计如下:

如上所述就实现了数码管的分时显示,四位数码管可以同时显示不同的数字。

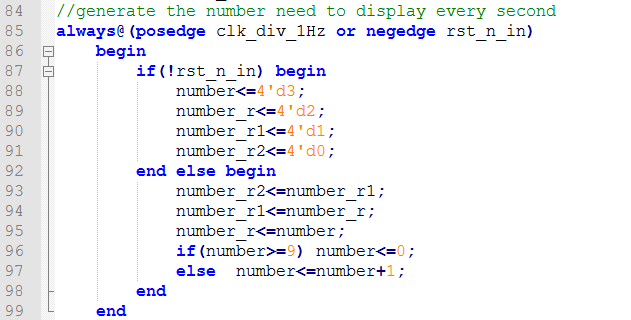

设计要求还需要按秒实现0到9循环左移显示,所以我们需要生成一个1Hz的信号clkdiv1Hz,然后由clkdiv1Hz触发完成显示内容的切换。

分频产生1Hz的时钟与上面产生6.4KHz信号的程序原理相同,这里不做赘述,然后基于1Hz时钟循环产生1~9的数据并使用寄存器逐级赋值锁存,方法如下:

引脚分配如下:

| 管脚名称 | clkin | rstnin | rclkout | sclkout | sdioout | |||

|---|---|---|---|---|---|

| FPGA管脚 | C1 | B1 | M1 | N2 | K1 |

系统运行

资源报告

| 资源 | 数量 | 比例 | 说明 |

|---|---|---|---|

| LUTs | 134 | 10% | |

| 寄存器 | 88 | 6% | |

| 存储器 | 0 | 0% | |

| IO管脚 | 5 | ||

| 时钟频率 | 25MHz |

知识点

- 时钟分频

- 串行/并行转换

- 数码管动态显示

参考文档

相关文档

| 文件名称 | 功能 |

|---|---|

| DLED_DISP | 数码管显示 |