**这是本文档旧的修订版!**

流水灯

====硬件平台====

====设计要求====

- 掌握分频功能的设计

- 掌握时序逻辑的设计

- 掌握case的基本语法

- 基于小脚丫STEP FPGA Base Board开发平台LED实现流水灯的功能,每个LED点亮时间为1秒

====工作原理====

本设计为流水灯实验,我们需要结合使用的硬件平台实现STEP-Baseboard平台上的8个LED循环闪烁,每个LED灯点亮时间为1秒。

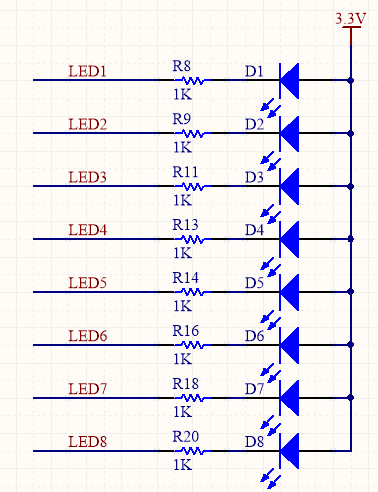

LED也叫发光二极管,属于二极管的一种,具有二极管的单项导电性,使用时需要给LED上施加正向压差,产生电流(一般在20mA以内,具体参考设计中使用的LED的参数),点亮LED。

为了使每个LED点亮1秒的时间,我们需要一个1Hz的信号,因为硬件平台STEP-MXO2第一代上使用的晶振为25MHz,2^25 = 33554432 > 25000000,所以我们需要做一个位宽为25的计数器。计数器初值为0,当计数到24999999时,总共计数25000000,也就是1秒时间。

为了实现流水的效果,我们需要一个寄存器,寄存器的值不同控制着不同的LED点亮,而寄存器的值在每次计数器计数到24999999时改变,这样每隔1秒时间,寄存器的值改变,对应控制8个LED按照同一方向循环闪烁,就实现了流水灯的功能。

====硬件连接====

结合实验平台STEP-Baseboard的硬件配置,我们使用8个LED灯作为流水灯的输出

====代码设计====

设计文件

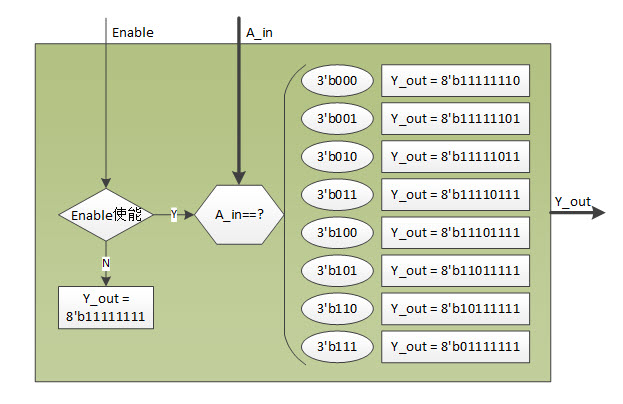

通过38译码器的原理及程序设计框图,我们不难发现这是一个比较简单的组合逻辑设计。

正如我们在原理及硬件连接中描述的,我们需要一路芯片使能端口、三路信号输入端口和八路信号输出端口。模块端口设计如下:

module Decode38 ( input Enable, input [2:0] A_in, output reg [7:0] Y_out );

逻辑部分,当芯片使能信号无效时,输出全部置高,当芯片使能信号有效时,根据三路信号的输入状态译码控制八路信号输出。

always@(A_in or Enable) begin if (Enable) case (A_in) 3'b000: Y_out = 8'b11111110; 3'b001: Y_out = 8'b11111101; 3'b010: Y_out = 8'b11111011; 3'b011: Y_out = 8'b11110111; 3'b100: Y_out = 8'b11101111; 3'b101: Y_out = 8'b11011111; 3'b110: Y_out = 8'b10111111; 3'b111: Y_out = 8'b01111111; default:Y_out = 8'b11111111; endcase else Y_out = 8'b11111111; end

测试文件

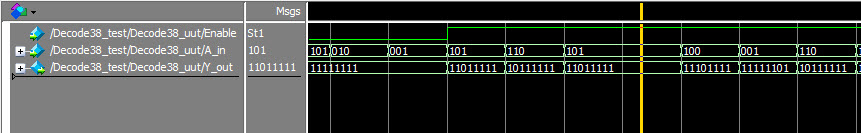

测试文件中,我们要生成被测文件输入信号需要的激励,我们设计Enable信号每隔200ns(200个时间单位)进行翻转,三路信号输入为每20ns取随机值($random)。

reg Enable; reg [2:0] A_in; initial begin Enable = 1'b0; A_in = 3'b000; end always Enable = #200 ~Enable; always A_in = #20 $random;

引脚分配如下:

| 管脚名称 | Enable | Ain[0]| Ain[1] | Ain[2] | Yout[0] | Yout[1] |Yout[2] | Yout[3] |Yout[4] | Yout[5] |Yout[6] | Y_out[7] | |||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| FPGA管脚 | P12 | M13 | M14 | N13 | B14 | C14 | E14 | F14 | G14 | J14 | K14 | L14 |

仿真结果

资源报告

| 资源 | 数量 | 比例 | 说明 |

|---|---|---|---|

| LUTs | 8 | 1% | |

| 寄存器 | 0 | 0% | |

| 存储器 | 0 | 0% | |

| IO管脚 | 12 | ||

| 时钟频率 | 25MHz |

知识点

- 组合逻辑

参考文档

相关文档

| 文件名称 | 功能 |

|---|---|

| Decode38.v | 38译码器 |

| Decode38_test.v | 测试文件 |