**这是本文档旧的修订版!**

=====比赛计分系统设计=====

实验任务

- 任务:基于 STEP-MAX10M08核心板 和 STEP BaseBoard V3.0底板 完成比赛计分系统设计并观察调试结果

- 要求:按动核心板独立按键,驱动底板上8位数码管为比赛双方在0~999内计分。

- 解析:FPGA驱动独立按键,当按动两队加分按键时,控制两队分数调整,最后通过驱动底板上的数码管电路将得分值显示在数码管上。

实验目的

在基础数字电路实验部分我们已经掌握了FPGA驱动独立按键的原理及方法,控制数码管显示十进制数的BCD码方案前面也多次介绍,本实验主要学习数码管扫描显示的原理及方法。

- 熟悉独立按键驱动模块的应用

- 了解数码管扫描显示的原理及方法

- 了解74HC595的工作原理及驱动方法

- 完成比赛计分系统设计实现

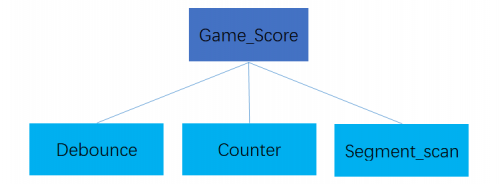

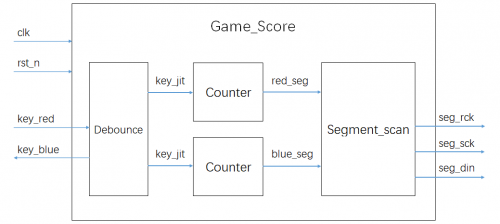

设计框图

根据前面的实验解析我们可以得知,该设计可以拆分成三个功能模块实现,

- Debounce:通过驱动独立按键工作获取操作信息数据。

- Counter:根据按键的操作信息控制双方比赛分值调整。

- Segment_scan:通过驱动串转并芯片74HC595控制数码管扫描显示比赛分值。

顶层模块Game_Score通过实例化三个子模块并将对应的信号连接,最终实现比赛计分系统的总体设计。

实验原理

数码管连接方式

数码管模块电路连接

数码管模块驱动设计

系统总体实现

实验步骤

- 双击打开Quartus Prime工具软件;

- 新建工程:File → New Project Wizard(工程命名,工程目录选择,设备型号选择,EDA工具选择);

- 新建文件:File → New → Verilog HDL File,键入设计代码并保存;

- 设计综合:双击Tasks窗口页面下的Analysis & Synthesis对代码进行综合;

- 管脚约束:Assignments → Assignment Editor,根据项目需求分配管脚;

- 设计编译:双击Tasks窗口页面下的Compile Design对设计进行整体编译并生成配置文件;

- 程序烧录:点击Tools → Programmer打开配置工具,Program进行下载;

- 观察设计运行结果。