1.7 T触发器

在本教程中,我们将学习另一种重要的触发器——T触发器。我们将了解其设计、工作原理以及一些T触发器的应用。

T触发器的设计

T触发器也被称为“翻转触发器”。为了避免SR触发器中出��现中间状态(也称为禁止状态),我们应该只向触发器提供一个输入,称为触发输入或翻转输入(T)。

此时,触发器作为一个翻转开关工作。翻转意味着“将下一个状态的输出切换为当前状态输出的反相”。

我们可以通过对JK触发器进行简单的修改来设计T触发器。T触发器是一个单输入设备,因此通过将J和K输入端连接在一起,并将它们与一个称为T的单输入相连,我们可以将JK触发器转换为T触发器。

因此,T触发器有时也被称为单输入JK触发器。

T触发器的逻辑符号如下所示。它有一个翻转输入(T)和一个时钟信号输入(CLK)。

T触发器的电路设计

我们可以通过以下方法构建T触发器:

- 使用SR触发器:将SR触发器的输出反馈连接到输入端。

- 使用D触发器:将T输入与Q的前一个输出通过异或门连接到D触发器的数据输入端。

- 使用JK触发器:将J和K输入端连接在一起,并将它们连接到T输入端。

使用SR触发器构建T触发器

我们可以通过将与门作为输入连接到或非门SR锁存器来构建T触发器。这些与门的一个输入是来自当前状态输出Q及其反相的反馈,分别连接到与R输入和S输入相关的与门,即Q连接到与R输入相关的与门,连接到与S输入相关的与门。

一个翻转输入(T)作为输入连接到两个与门。与门还连接到一个公共的时钟(CLK)信号。

在T触发器中,提供一串窄脉冲作为输入(T),这将导致触发器输出状态的改变。因此,这些触发器也被称为翻转触发器。使用SR锁存器构建的T触发器的电路图如下所示。

使用D触发器构建T触发器

类似地,我们可以通过修改D触发器来构建T触发器。在D触发器中,输出Q与T输入通过异或门连接,并作为D输入。使用D触发器构建的T触发器的逻辑图如下所示。

使用JK触发器构建T触发器

构建T触发器最简单的方法是使用JK触发器。将JK触发器的J输入和K输入端连接在一起,并将它们连接到T输入端。使用JK触发器构建的T触发器的电路图如下所示。

T触发器的工作原理

T触发器是一种边沿触发设备,即输入时钟信号的低到高或高到低的转换将导致触发器输出状态的改变。

T触发器的真值表

T触发器的真值表如下所示。

| T | ||

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

如前所述,T触发器是一种边沿触发设备。例如,考虑一个由与非门SR锁存器构成的T触发器,如下所示。

如果输出Q = 0,则上层与非门(与非门C)处于禁用状态(没有主导输入),而下层与非门(与非门D)处于启用状态(来自Q的反馈是主导输入)。这意味着翻转输入将为RS锁存器设置输入条件为R = 1和S = 0。如果你回忆RS锁存器的真值表,这个条件将置位输出。因此,Q变为1。

如果输出Q = 1,则上层与非门处于启用状态,而下层与非门处于禁用状态。这允许翻转输入为RS锁存器设置输入为R = 0和S = 1。这将使触发器复位,即Q = 0。

简单来说,T触发器的工作原理如下:

- 当T输入为低电平时,T触发器的下一个状态与当前状态相同。

- T = 0且当前状态 = 0,则下一个状态 = 0

- T = 0且当前状态 = 1,则下一个状态 = 1

- 当T输入为高电平且在时钟信号的正向转换期间,T触发器的下一个状态是当前状态的反相。

- T = 1且当前状态 = 0,则下一个状态 = 1

- T = 1且当前状态 = 1,则下一个状态 = 0

由于每个输入触发信号交替地改变置位和复位输入,触发器进行翻转。因此,完成一个完整的输出波形周期需要两个触发信号。这意味着T触发器的输出频率正好是输入频率的一半。因此,T触发器可以作为“频率分频电路”。

T触发器的主要缺点是,只有在已知先前状态的情况下,才能知道在应用触发脉冲时触发器的状态。

通常,T触发器不作为集成电路(IC)提供。因此,我们可以通过使用JK触发器、SR触发器和D触发器来构建T触发器。使用JK触发器构建的T触发器的符号如下所示。

T触发器的应用

现在,让我们来看一些T触发器的重要应用。

频率分频电路

通过将互补输出反馈到T输入,T触发器可以用作“频率分频电路”。使用T触发器的频率分频电路的逻辑符号如下所示。

如果T触发器的输入时钟频率为赫兹,则输出Q的脉冲频率为赫兹。我们可以通过级联多个这样的频率分频电路来进一步分频。

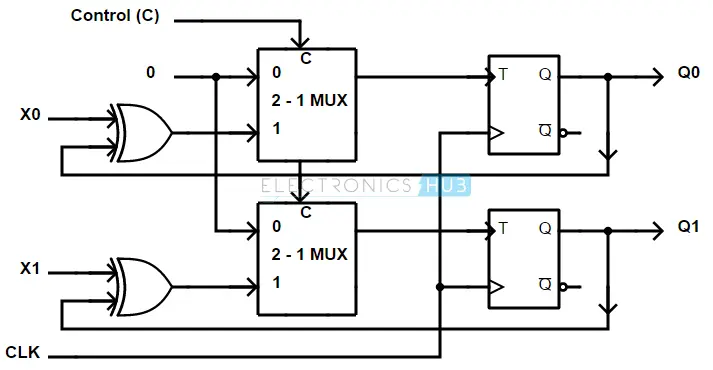

使用T触发器的2位并行加载寄存器

我们使用寄存器和移位寄存器来存储数据。但对于存储元件(如寄存器)来说,尺寸始终是一个主要问题。因此,我们使用2位并行加载寄存器而不是4位寄存器。

在设计并行加载寄存器时,需要考虑两个操作:

- 保持数据

- 并行加载数据

为了保持T触发器的输出,只需将输入T设为0。但并行加载是一个较难的部分。

并行加载意味着在触发器的输出处获得值X。为了实现这一点,我们将X输入和当前状态输出进行异或操作,并将其连接到2选1多路复用器(MUX)。MUX的另一个输入是一个恒定的0(低电平)。MUX的输出连接到T触发器的输入。

由于这是一个2位寄存器,因此需要两个这样的组合。2位并行加载寄存器的电路如下所示。