1.8 BCD到7段显示解码器

七段显示器通常用于显示数字手表、计算器、时钟、测量仪器和数字计数器等设备中的数字。通常,LED 和 LCD 段提供数值和字符的显示输出。

然而,为了显示字符和数字(以产生十进制读数),七段显示器被最广泛使用。这些显示器通常由数字集成电路(IC)的输出级驱动(需要对输出级进行视觉指示),例如锁存器和十进制计数器等。

但这些输出是以 4 位二进制编码的十进制(BCD)形式,不适合直接驱动七段显示器。

显示解码器

显示解码器用于将 BCD 或二进制代码转换为 7 段代码。它通常有 4 个输入线和 7 个输出线。在这里,我们使用逻辑门设计一个简单的显示解码器电路。

尽管有现成的 BCD 到 7 段解码器可供使用,但从经济和知识角度来看,使用逻辑门设计显示解码器可能会更有益。

显示解码器电路原理

基本思想是使用组合逻辑电路驱动一个共阴极 7 段 LED 显示器。逻辑电路设计有 4 个输入和 7 个输出,每个输出代表一个输入到显示 IC 的信号。使用卡诺图(Karnaugh Map),为每个输入到显示器设计逻辑电路。

电路背后的理论

解码器是这个电路的核心部分。解码器是一种组合逻辑电路,用于将二进制或 BCD(二进制编码的十进制)数字转换为对应的十进制数字。它可以是一个简单的二进制到十进制解码器,也可以是一个 BCD 到 7 段解码器。

另一个相关部分是组合逻辑电路。组合逻辑电路是由逻辑门组成的系统,只包含输入和输出。组合逻辑电路的输出仅取决于输入的当前状态,而与输入的历史状态无关。这种电路的最佳例子包括编码器和解码器、多路复用器和解复用器、加法器、减法器等。

要理解这些逻辑电路的设计和操作,需要对布尔代数和逻辑门有良好的了解。例如,需要遵循的一些基本布尔代数规则包括互补律、结合律和德摩根定律等。

7 段 LED 显示器由 8 个 LED 组成,这些 LED 以“H”形排列,所有阳极或阴极可以是共用的。共阴极 7 段显示器有 8 个引脚——7 个输入引脚,标记为“a”到“g”,以及第 8 个引脚作为公共地引脚。

7 段显示器解码器电路设计

步骤 1:分析共阴极 7 段显示器 7 段显示器由以“H”形排列的 LED 组成。为每个十进制数字构建输入组合的真值表。例如,十进制数字 1 将命令 b 和 c 的组合(参见下图)。

步骤 2:构建真值表 列出 7 个显示输入信号、十进制数字及其对应的 4 位二进制数字的真值表。

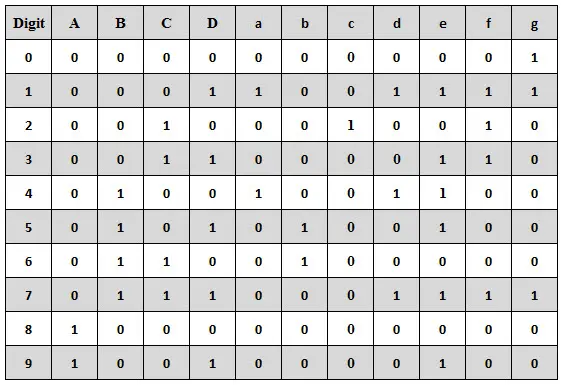

BCD 到 7 段解码器真值表

解码器设计的真值表取决于 7 段显示器的类型。如上所述,对于共阴极七段显示器,解码器或段驱动器的输出必须是高电平有效,才能点亮段。

下图展示了共阴极显示器的 BCD 到七段解码器的真值表。在真值表中,有 7 个不同的输出列,分别对应于 7 个段中的每一个。

假设段 a 的列显示了它被点亮的不同组合。因此,对于数字 0、2、3、5、6、7、8 和 9,“a” 是激活的。

从上述真值表中,可以写出每个输出函数的 7 段显示器布尔表达式:

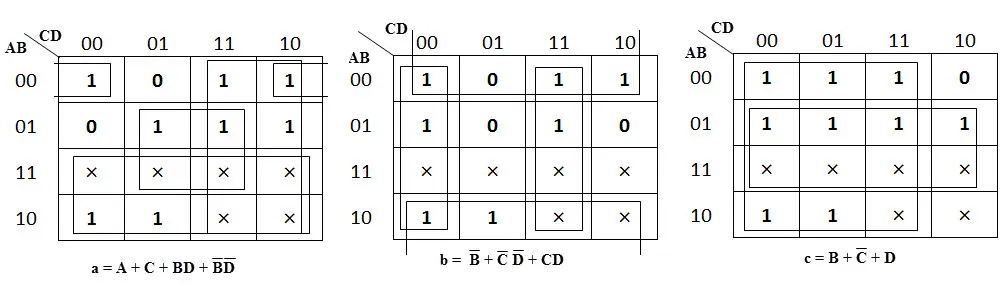

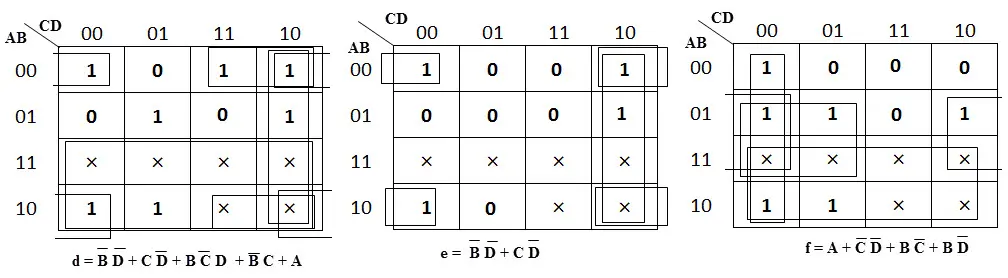

步骤 3:卡诺图简化 为每个输出项构建卡诺图,然后简化它们以获得每个输出的输入逻辑组合。

7 段显示器卡诺图简化

下图展示了共阴极七段解码器的 7 段卡诺图简化,以设计组合电路。

从上述简化中,我们得到输出值如下:

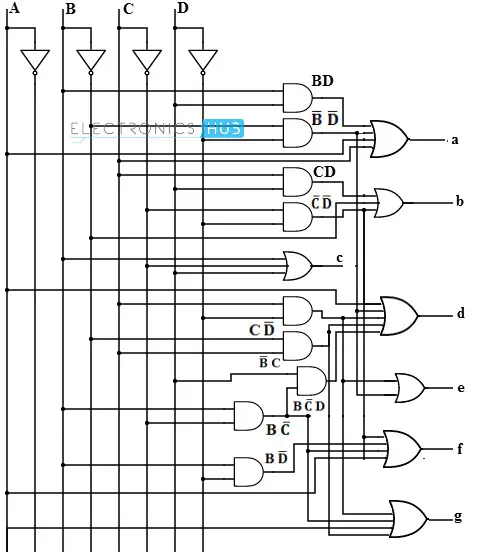

步骤 4:绘制组合逻辑电路 一旦完成上述步骤,可以使用 4 个输入(A、B、C、D)和 7 段显示器(a、b、c、d、e、f、g)作为输出,绘制组合逻辑电路。

显示解码器电路操作

通过真值表可以理解电路的操作。当所有输入连接到低电平时,组合逻辑电路的输出将驱动所有输出 LED 除“g”之外的导通。因此,将显示数字 0。对于所有其他输入开关的组合,将进行类似的操作。

实际上,BCD 到 7 段解码器以集成电路形式存在,例如 74LS47。除了常规的 4 个输入引脚和 7 个输出引脚外,它还包括一个用于段测试的灯测试引脚、一个用于在多显示器系统中消隐零的逐位消隐输入引脚、一个用于级联目的的逐位消隐输出引脚和一个消隐输入引脚。

显示解码器电路的应用

- 该电路可以通过使用定时器和计数器修改,以显示时钟脉冲的数量。

- 该电路可以修改为开发字母显示系统,而不是十进制数字显示系统。

- 它可以用作定时器电路。

显示解码器电路的局限�性

- 该电路涉及许多逻辑门,相当复杂。

- 每个逻辑门的延迟是一个问题,当用于显示脉冲计数时,该电路可能无法产生准确的结果。

- 这是一个理论电路,可能需要一些修改。