1.6结场效应晶体管

在本教程中,我们将学习一种称为结型场效应晶体管(JFET)的场效应晶体管(FET)变体。我们将了解其电路符号、基本偏置条件、伏安特性、简单的放大电路以及一些应用。

引言

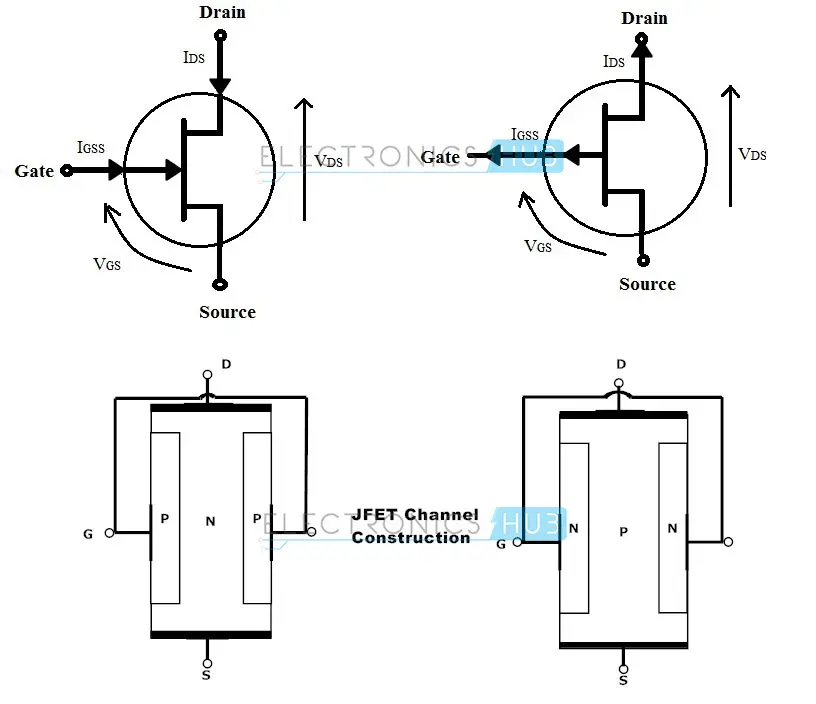

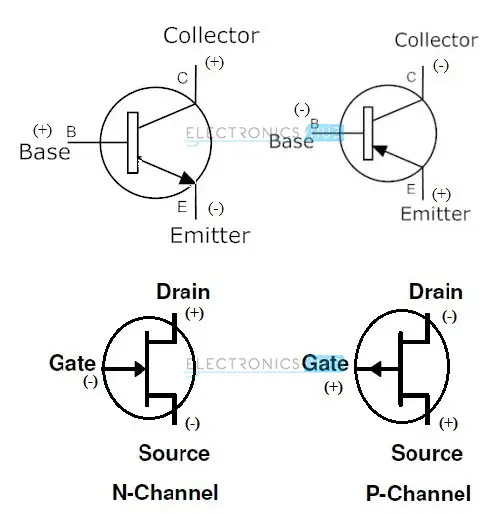

FET晶体管是电压控制器件,而BJT晶体管是电流控制器件。FET晶体管基本上有三个端子:漏极(D)、源极(S)和栅极(G),它们分别对应于BJT晶体管中的集电极、发射极和基极。

在BJT晶体管中,输出电流由输入到基极的电流控制,而在FET晶体管中,输出电流由输入到栅极的电压控制。

在FET晶体管中,输出电流在漏极和源极之间流动,这条路径称为沟道,沟道可以由P型或N型半导体材料制成。在BJT晶体管中,小的输入电流控制大的负载,而在FET中,小的输入电压控制大的负载输出。

BJT晶体管是“双极”器件,因为它们使用两种类型的电荷载流子(电子和空穴)工作,而FET晶体管是“单极”器件,因为它们只使用一种电荷载流子(N沟道为电子,P沟道为空穴)。

FET晶体管可以做得比BJT晶体管更小,并且功耗更低。由于这种高效率,FET晶体管在许多电子电路应用中取代了相应的BJT晶体管。这些FET晶体管由于其低功耗特性,在芯片设计中非常有用。与BJT一样,FET晶体管也有P沟道和N沟道两种类型。

FET晶体管具有高输入阻抗,而BJT的输入阻抗相对较低。由于这种高阻抗值,FET晶体管对小的输入电压非常敏感。FET晶体管主要分为两种类型:结型场效应晶体管(JFET)和绝缘栅FET(IG-FET)或金属氧化物半导体FET(MOSFET)。

JFET简介

结型场效应晶体管(JFET)是FET晶体管的一种类型。JFET是FET晶体管的最简单形式,它有三个端子。JFET晶体管用作电子控制开关、电压控制电阻器和放大器。

BJT晶体管由PN结构成,而JFET晶体管有一个沟道代替PN结。这个沟道由P型或N型半导体材料形成。

JFET晶体管分为两种类型:N沟道JFET和P沟道JFET。在N沟道JFET中,沟道掺杂了施主杂质,因此通过沟道的电流是负的(即由电子引起),而在P沟道JFET中,沟道掺杂了受主杂质,因此通过沟道的电流是正的(即由空穴引起)。

N沟道JFET的导电性比P沟道JFET更好,因为电子的迁移率高于空穴。因此,N沟道JFET比P沟道JFET更常用。栅极(G)端子上的小电压控制JFET沟道(漏极和源极之间)中的电流流动。

在BJT中,发射极和集电极端子通过PN结连接,但在JFET中,漏极和源极端子通过沟道连接。施加在栅极端子上的小电压控制JFET漏极和源极之间沟道中的电流流动。在N沟道JFET中,栅极电压为负,在P沟道JFET中,栅极电压为正。

BJT和JFET晶体管的主要区别之一是,当JFET具有反向偏置结时,栅极电流可能为零,但在BJT中,基极电流必须始终大于零。

N沟道JFET偏置

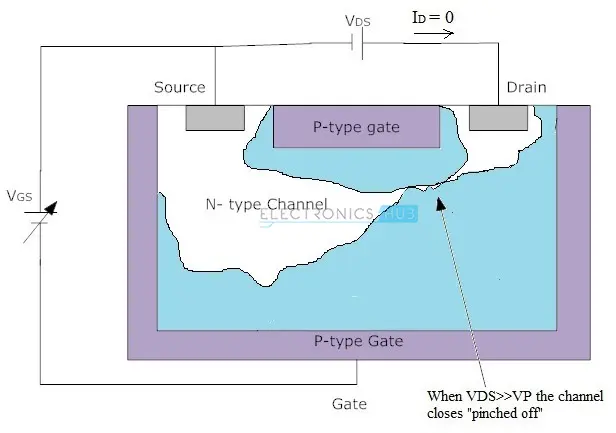

N沟道JFET晶体管的内部图如下所示。这是一个具有N型沟道和P型区域的晶体管。如果栅极扩散到N型沟道中,则形成反向偏置的PN结,当晶体管没有外部电源施加时,在栅极端子周围形成耗尽区。通常,JFET被称为耗尽型器件。

这个耗尽区在PN结周围产生厚度变化的电势梯度。这个PN结通过减小沟道宽度和增加沟道电阻来阻止电流通过沟道。

现在,JFET的沟道在零偏置电压输入下导通。因为在栅极-漏极之间形成了大部分耗尽区,而在栅极-源极之间形成了小部分耗尽区。

如果在漏极-源极之间施加小电压 ,栅极电压为零 ,则电流 将通过沟道流动。现在,如果我们施加少量负电压 (即反向偏置条件),则耗尽区宽度增加,导致沟道长度部分减少,沟道导电性降低。

这个过程称为“挤压效应”。如果我们在栅极端子施加更多的负电压,则会减小沟道宽度,直到没有电流流过沟道。在这种条件下,JFET被称为“夹断”。使FET沟道关闭的施加电压称为“夹断电压 ”。

夹断效应

具有N沟道结构的JFET如上所示。最初,如果栅极电压为零,则沟道电阻也为零,沟道导电性高。如果栅极电压(即负电压)增加到零以上,则沟道电阻也增加,少量电流将通过沟道流动。

如果我们在栅极端子施加大量负电压,则沟道完全阻止电流通过。在这种条件下,沟道中没有电流流动,现在JFET充当一个完美的电阻器。

JFET沟道关闭的状态称为“夹断”,这种情况下的栅极电压称为“夹断电压 ”。在夹断条件下,栅极电压 控制沟道电流。P沟道JFET的操作与N沟道JFET相同,但有一些变化,例如沟道电流是正的,因为空穴导电,并且需要反向极性来施加栅极电压。

JFET的伏安特性

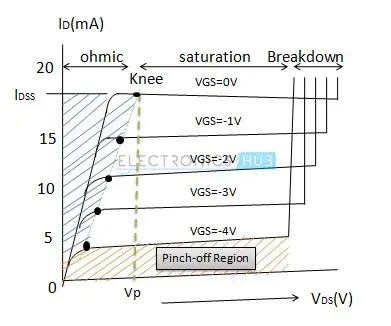

N沟道JFET的伏安特性如下所示。在这种N沟道JFET结构中,栅极电压 控制源极和漏极之间的电流流动。JFET是电压控制器件,因此没有电流流过栅极,源极电流 等于漏极电流 ,即 。

在这种伏安特性中,电压 表示栅极和源极之间施加的电压,电压 表示漏极和源极之间施加的电压。

JFET在不同工作阶段具有不同的特性,具体取决于输入电压,JFET在不同区域(欧姆区、饱和区、截止区和击穿区)的特性如下:

- 欧姆区:如果 ,则沟道的耗尽区非常小,在此区域JFET充当电压控制电阻器。

- 夹断区:这也称为截止区。当栅极电压为大的负电压时,JFET进入此区域,沟道关闭,即没有电流流过沟道。

- 饱和区或放大区:在此区域,沟道充当良好的导体,由栅极电压 控制。

- 击穿区:如果漏极到源极电压 足够高,则JFET的沟道击穿,在此区域,不受控制的最大电流通过器件。

P沟道JFET晶体管的伏安特性曲线与N沟道JFET相同,但有一些例外,例如如果栅极到源极电压 正向增加,则漏极电流减小。

当施加的电压 等于夹断电压 时,流过沟道的漏极电流 为零。在JFET的正常操作中,施加的栅极电压 在0和 之间,在这种情况下,流过沟道的漏极电流 可以计算如下:

其中:

- 为漏极电流

- 为最大饱和电流

- 为栅极到源极电压

- 为夹断电压

漏源电阻等于漏源电压变化率与漏极电流变化率的比值:

其中:

- 为漏源电阻

- 为漏极到源极电压

- 为漏极电流

- 为跨导增益

JFET共源放大器

与BJT晶体管一样,FET晶体管也用于设计单级A类放大器。JFET的共源放大器类似于BJT晶体管的共发射极放大器。JFET相对于BJT的优势在于其高输入阻抗。

由电阻 和 形成的偏置网络的共源放大器电路如下所示。

这是一个偏置在A类模式的共源放大器电路。所需的栅极电压使用 值计算。通常,源极电阻上的电压设置为 的四分之一,即 。我们需要通过适当选择电阻 和 来设置直流静态电压。

在这里,漏极电流由负栅极电压控制。在N沟道JFET晶体管中,栅极从不包含正电压,因为漏极电流通过栅极流动,而不是通过源极流动,导致JFET损坏。

如果电压极性反转,P沟道JFET放大器电路的操作也与N沟道JFET类似。计算共源放大器电路不同参数的方程如下:

其中:

- 为源极电压

- 为漏极电流

- 为源极电阻

- 为漏极电源电压

- 为栅极电压

- 为栅极到源极电压

- 和 为偏置电阻

JFET应用

- JFET用作开关。

- JFET用作斩波器。

- 用作放大器。

- 用作缓冲器。

- 由于其低频漂移,用于振荡电路。

- 由于其小尺寸,用于数字电路,如计算机、LCD和存储电路。

- 由于其低调制失真,用于通信设备,如FM和TV接收器。

- 用作运算放大器中的电压控制电阻器。

- JFET用于级联放大器和射频放大器。