7.1实验二十一 智力竞赛抢答器

7.1.1 实验目的

(1)熟悉和掌握FPGA开发流程和Lattice Diamond软件使用方法;

(2)通过实验理解和掌握抢答器原理;

(3)学习用Verilog HDL描述方法描述抢答器。

7.1.2实验任务

本实验的任务是设计一个智力竞赛抢答器,带复位和主持人控制功能。

1,一共4组选手,用开关k1,k2,k3,k4表示,

2,主持人复位开始抢答,获得抢答的选�手显示对应led,答题时间超过30秒报警

3,每位选手初始分数5分(RESET复位),主持人控制加分减分按键,每次增加或减少1分(最多9分),答题选手分数显示在数码管

7.1.3实验原理

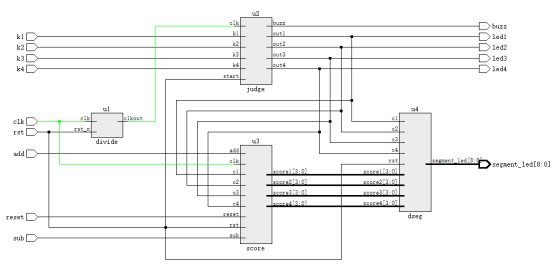

根据抢答器的功能,采用模块化设计,如下

抢答判断模块(judge):根据开关的输入判断抢答的选手信号,通过输出的LED显示抢答选手;内部定义block标志信号用来锁定抢答完成;判断抢答之后答题超过30秒产生报警信号。

分数模块(score):复位信号单独复位所有选手分数;加减按键消抖后用来增加减少分数。

显示模块(dseg):当前抢答的选手分数显示在数码管上。

分频模块(divide):分频产生计时时钟信号。

7.1.4Verilog HDL建模描述

程序清单answer.v

module answer

(

input wire clk,rst, //时钟和复位信号

input wire k1,k2,k3,k4, //选手开关

input wire reset,add,sub, //复位分数,加分,减分按键

output wire led1,led2,led3,led4,//选手对应led

output wire buzz, //报警信号

output wire [8:0] segment_led //数码管信号

);

wire clk1h;

divide #( //产生1秒时钟信号

.WIDTH(24),

.N(12000000)

) u1

(

.clk(clk),

.rst_n(rst),

.clkout(clk1h)

);

judge u2 //判断抢答选手,答题超时报警

(

.clk(clk1h),

.k1(k1),.k2(k2),.k3(k3),.k4(k4),

.start(rst),

.out1(led1),.out2(led2),.out3(led3),.out4(led4),

.buzz(buzz)

);

wire [3:0] score1,score2,score3,score4;

score u3 //主持人控制答题选手分数

(

.clk(clk),.rst(rst),

.add(add),.sub(sub),

.reset(reset),

.c1(led1),.c2(led2),.c3(led3),.c4(led4),

.score1(score1),.score2(score2),.score3(score3),.score4(score4)

);

dseg u4 //数码管驱动显示答题选手分数

(

.rst(rst),

.c1(led1),.c2(led2),.c3(led3),.c4(led4),

.score1(score1),.score2(score2),.score3(score3),.score4(score4),

.segment_led(segment_led)

);

endmodule

顶层文件一共调用了4个模块judge.v、score.v、dseg.v、divide.v。所有的子模块源码请参考实验二十一的工程文件

7.1.5实验步骤

1.打开Lattice Diamond,建立工程。

2.新建Verilog HDL设计文件,并键入设计代码。

3.根据逻辑综合并分配管脚,在本实验中引脚分配如下:

| 信号 | 引脚 |

|---|---|

| key[1:4] | M7, M8, M9, M10 |

| clk | C1 |

| rst | L14 |

| reset | N14 |

| add | M13 |

| sub | M14 |

| buzz | P9 |

| led[1:4] | N13, M12, P12, M11 |

| segment[8:0] | A12~C12 |

4构建并输出编程文件,烧写至FPGA的Flash之中。

5.观察输出结果。

当程序下载成功时,按下rst复位,表示抢答开始。由于开发板上的开关有限,所以采用四个拨码开关分别表示4个抢答选手。��当判断拨码开关状态后,同时该选手对应的led点亮。

按下reset复位键,抢答完成后在数码管上显示选手分数,可以通过加减分按键修改分数。