3.9实验九 密码锁

3.9.1 实验目的

(1)熟悉和掌握FPGA开发流程和Quartus软件使用方法;

(2)通过实验理解和掌握密码锁原理;

(3)学习用Verilog HDL行为级描述方法描述密码锁电路。

3.9.2实验任务

设计4位二进制密码锁,要求如下:

4位密码输入代码分别为Q、U、N、B,开箱时,钥匙插入钥匙孔右旋使D=1,如果输入密码(如:QUNB=0101)与设置的代码相同,则保险箱被打开,即输出端G=1,否则箱体发出报警。

3.9.3实验原理

根据任务要求可知,只有当D=1,且输入密码=0101时,输出G=1,报警器W=0。其他情况下D=1,输出G=0,报警器W=1。若D=0, 输出G=0,报警器W=0。密码锁真值表如下:

表2-1 密码锁真值表

| D | Q | U | N | B | G | W | Y |

|---|---|---|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 |

| 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

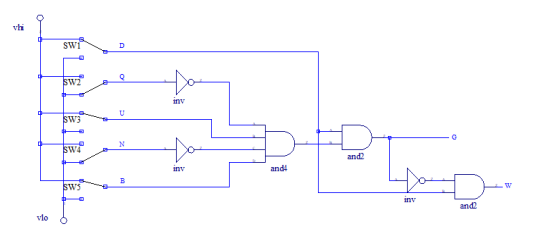

3.9.4 逻辑电路图

3.9.5 Verilog HDL建模描述

4位密码锁程序清单coded_lock.v

module coded_lock

(

input wire q,u,n,b, //四位开关作为密码输入

input wire d, //一位按键作为开锁使能信号

output wire led1, //保险箱打开信号对应的led输出

output wire led2 //报警信号对应的led输出

);

wire [3:0] code; //四位变量存储密码

reg open; //保险箱开箱信号

reg alarm; //报警信号

assign code = {q,u,n,b};

always@(d or code)

if(d == 1'b1) //使能,开始判断密码

begin

if(code == 4'b0101)

begin

open = 1'b1; //开锁

alarm = 1'b0; //没报警

end

else

begin

open = 1'b0;

alarm = 1'b1;

end

end

else

begin

open = 1'b0;

end

assign led1 = ~open; //led亮表示密码锁没开

assign led2 = ~alarm; //led亮代表发出报警信号

endmodule

3.9.6 实验步骤

1.打开Quartus,建立工程。

2.新建Verilog HDL设计文件,并键入设计代码。

3.综合并分配管脚,将输入信号d,q,u,n,b分配至拨码开关,将输出信号led1,led2分配至板卡上的LED。

| 信号 | FPGA PINs |

|---|---|

| d | J9 |

| q | J12 |

| u | H11 |

| n | H12 |

| b | H13 |

| led1 | N15 |

| led2 | N14 |

4.构建并输出编程文件,烧写至FPGA的Flash之中。

5.观察输出结果。

开发板按键开关低电平有效,所以d的常态是1,表示插入钥匙旋转。此时,我们可以通过改变拨码开关,观察两灯的变化。只有当拨码开关拨至0101时,led1亮,led2灭,表示输出有效,不报警。其他拨码状态代表输入密码错误,led1灭,led2亮,输出无效,报警。

若按下d所连接的按键开关L14使d=0,表示未插入钥匙,此时无论输入何密码,输出和报警都会无效,两个led 灯均不会亮。以上过程,达到了密码锁的功能。