4.1.0 实验介绍

实验简介

本教程以实验为主,结合相应的实验案例,以详细的讲解和实验步骤让大家尽快熟悉FPGA开发的基本流程、Ridiant软件平台的使用方法以及本节实验相关模块的工作原理。

- 熟悉和掌握FPGA开发的基本流程

- 掌握Ridiant软件平台的基本使用方法

- 了�解使用DS18B220的原理

- 掌握使用Verilog HDL语言基于FPGA实现DS18B20测量温度的原理及实现方法

背景知识

温度传感器(temperature transducer)是指能感受温度并转换成可用输出信号的传感器,是各种传感器中最常用的一种。早期的温度传感器是采集热敏电阻等元器件的电压,再根据给定公式计算出环境温度。随着现代仪器的发展,美国DALLAS半导体公司推出的数字化温度传感器DS18B20采用单总线协议,即与FPGA接口仅需占用一个I/O端口,无须任何外部元件,直接将环境温度转化成数字信号,以数字码方式串行输出,从而大大简化了传感器与FPGA的接口设计。

DS18B20测量温度的范围是-55°C~+125°C,精度为±0.5℃。外部环境的温度会转化为912位数据形式以单总线的方式传输。它的工作电压为35.5v。

DS18B20采用1-Wire总线协议,该总线协议仅需要一个控制信号进行通信。该控制信号线需要一个唤醒的上拉电阻以防止连接在该总线上的口是3态或者高阻态(DQ信号线是在DS18B20上)。在该总线系统中,微控制器(主设备)通过每个设备的64为序列号来识别该总线上的设备。因为每个设备都有一个独一无二的序列号,挂在一个总线上的设备理论上是可以无限个的。

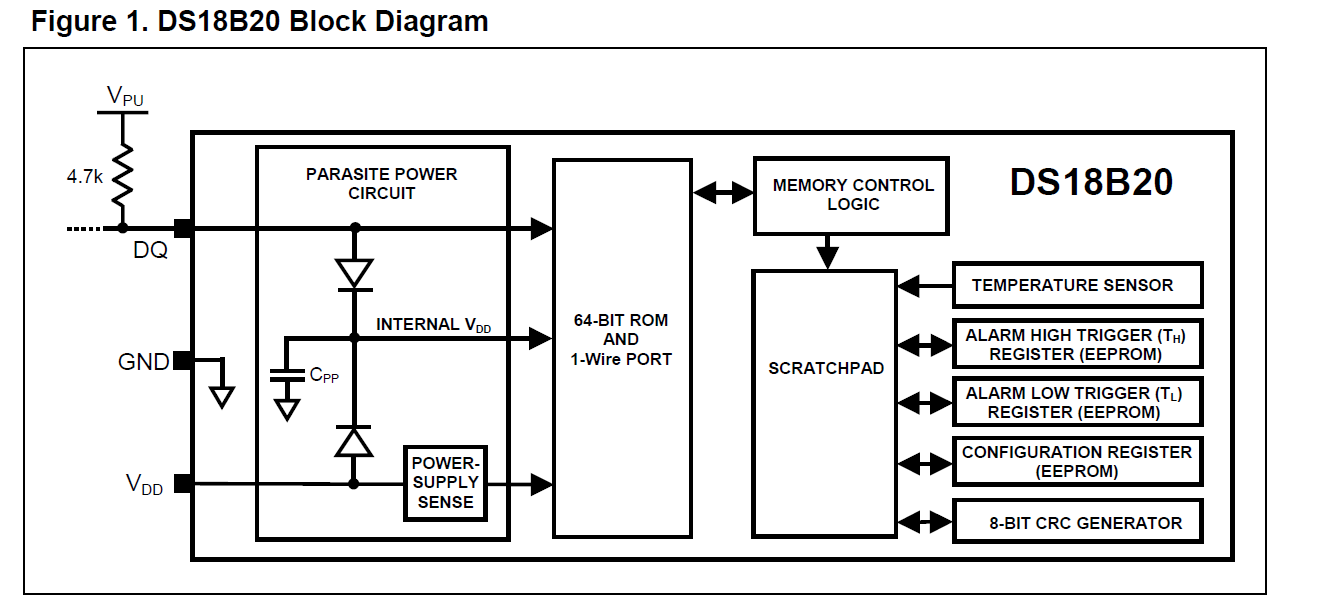

DS18B20的另外一个特性就是可以无需外部电源供电。当数据线DQ为高的时候由其为设备供电。总线拉高的时候为内部电容(Spp)充电,当总线拉低是由该电容向设备供电。这种由1-Wire总线为设备供电的方式称为“寄生电源”。此外,DS18B20也可以由外部电源通过VDD供电。DS18B20内部框图如下所示:

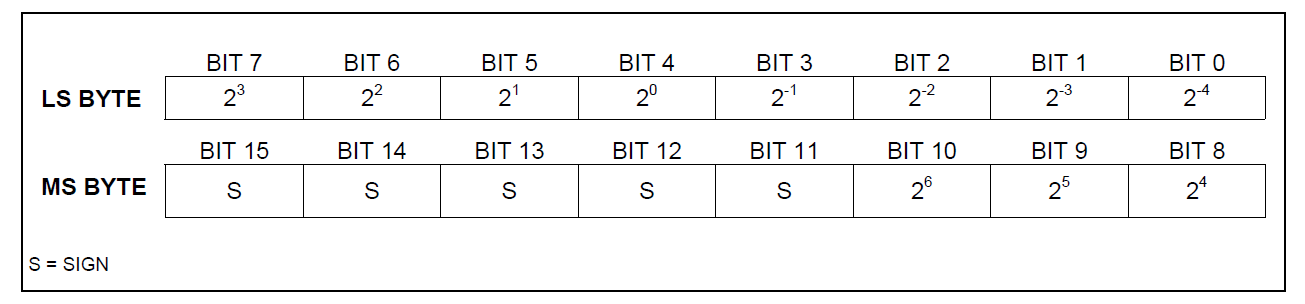

DS18B20的核心功能是直接温度—数字测量,上电后工作在低功耗闲置状态下,其温度转换可由用户自定义为9、10、11、12位精度分别为0.5℃、0.25℃、0.125℃、0.0625℃分辨率,上电默认为12位转换精度。温度数据以一个16位标志扩展二进制补码数的形式存储在温度寄存器中,符号标志位(S)温度的正负极性:正数则S=0,负数则S=1。如果DS18B20被定义为12位的转换精度,温度寄存器中的所有位都将包含有效数据。若为11位转换精度,则BIT 0为未定义的。若为10位转换精度,则BIT 1和BIT 0为未定义的。 若为9位转换精度,则BIT 2、BIT 1和BIT 0为未定义的。下表为在12位转换精度下温度输出数据与相对应温度之间的关系表。

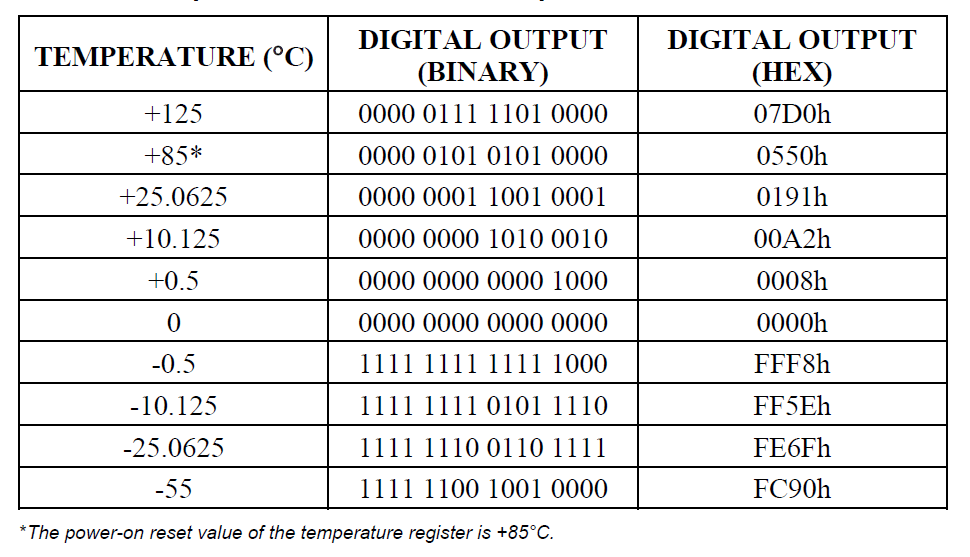

下表为一些在12位输出时的温度和对应的输出数据的例子。

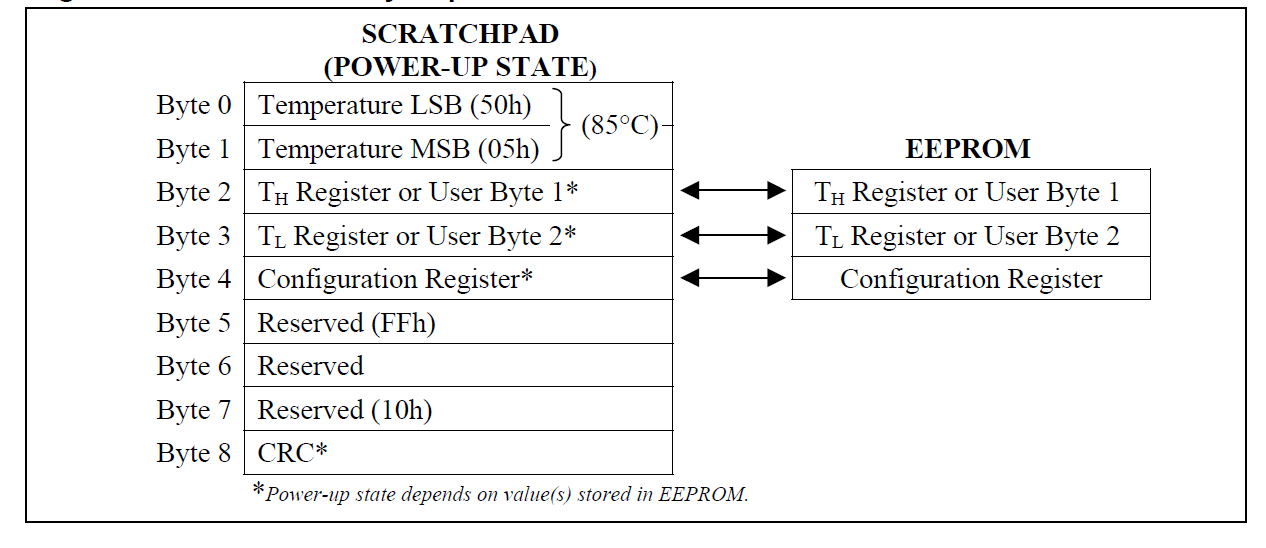

DS18B20存储器包含了SRAM暂存寄存器、过温和低温(TH和TL)温度报警寄存器、配置寄存器的非易失性EEPROM。当温度报警功能没有用到的时候,过温和低温(TH和TL)温度报警寄存器可以当做通用功能的存储单元。

SRAM暂存寄存器中的Byte 0和Byte 1分别作为温度寄存器的低字节和高字节,同时这两个字节是只读的;Byte 2和Byte 3作为过温和低温(TH和TL)温度报警寄存器;Byte 4保存着配置寄存器的数据;Byte 5、6、7作为内部使用的字节而保留使用,不可被写入;Byte 8存�储着该暂存寄存器中Byte 0至Byte 7的循环冗余校验(CRC)值,并且只读不可写入,存储器组织结构如下图所示:

在了解了一些DS18B20的基础知识之后,那么我们该如何使用单总线方式发送和接受数据呢?

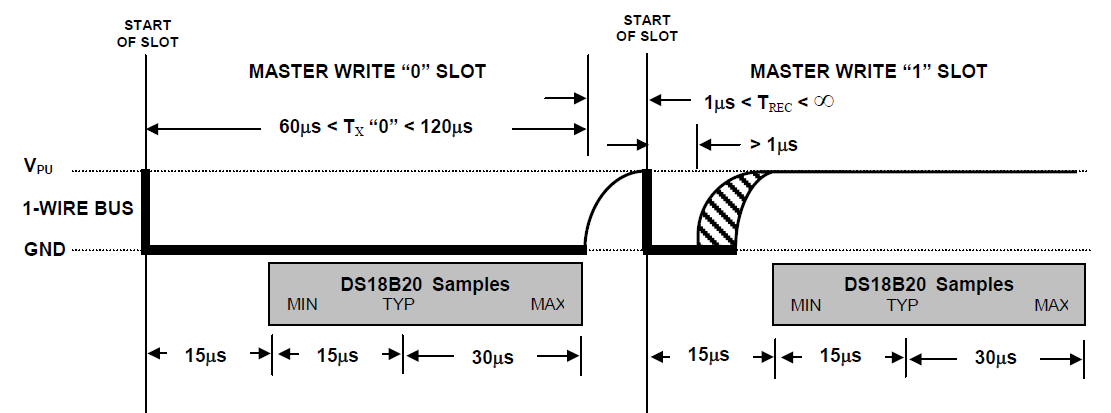

写时隙有两种:写0,写1。下图为写时隙的时序图,所有的写时隙至少需要60us,并且两次写时隙之间至少需要1us的恢复时间。两种写时隙均在主机拉低数据总线后来时。写0:数据总线拉低保持至少60us即可;写1:在主机拉低数据总线后,必须在15us之内拉高数据总线。因为单总线器件会在写时隙开始后的15~60us采样,如在此器件数据总线为高电平,则写1;如为低电平,则写0。

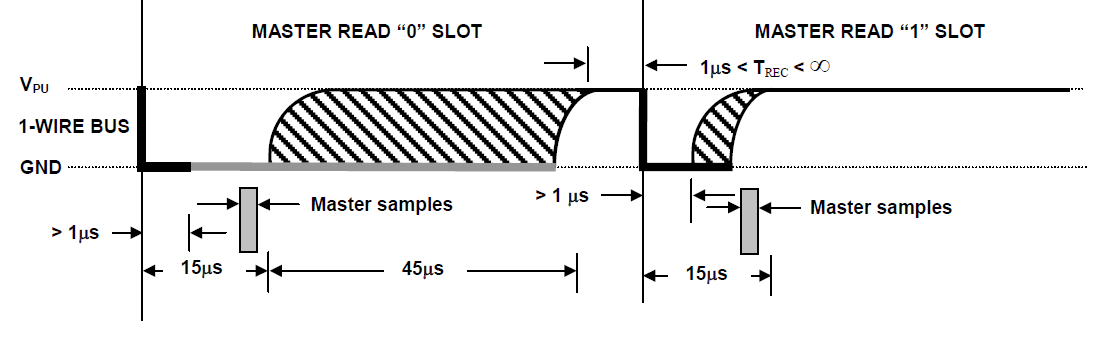

对于读时隙,单总线器件仅在主机发出读数据命令后,才向主机传输数据。主机发出读数据命令后,必须马上产生读时隙,以便从机能够传输数据。读时隙也有两种:读0,读1。下图为读时隙的时序图,所有的读时隙至少需要60us,并且两次读时隙之间至少需要1us的恢复时间。每个读时隙由主机发起,至少拉低1us的数据总线。由于从机发送的数据有效时间是15us,所以主机必须在15us时间内采样数据总线的状态。读0:在15us采样数据总线状态为低电平;读1:在15us内采样数据总线状态为高电平。

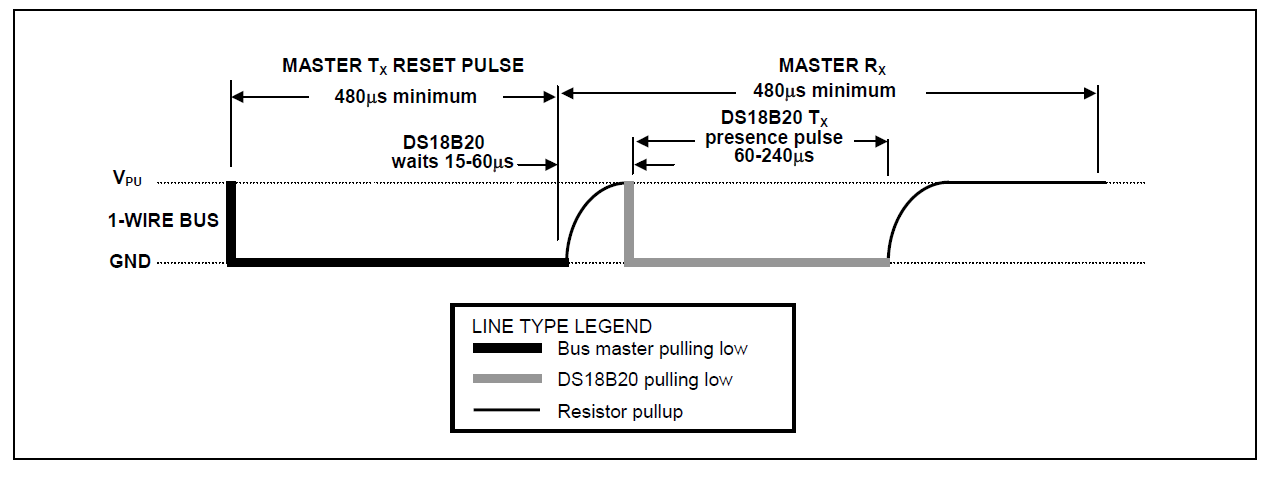

下图为DS18B20的初始化时序,主机拉低数据总线并保持480us960us,此时为主机发送复位脉冲。然后主机释放总线,保持1560us。然后DS18B20会拉低数据总线并保持60~240us,此时是DS18B20向主机发送的应答信号。从主机释放总线到DS18B20发送应答信号至少要480us。等到应答完成后,初始化结束。

对于简单的使用FPGA从DS18B20读取温度,其实要经历以下过程:为:初始化发跳过ROM命令(CCH)发开始转换命令(44H)延时初始化发送跳过ROM命令(CCH)发读存储器命令(BEH)连续读出两个字节数据(即温度)结束或开始下一循环。

实验环境

- 硬件环境:STEP FPGA 实验平台

- 软件环境:Ridiant开发环境