环形计数器

1. 实验目的

- (1)熟悉和掌握FPGA开发流程和Lattice Diamond软件使用方法;

- (2)通过实验理解和掌握环形计数器原理;

- (3)学习用Verilog HDL行为级描述时序逻辑电路。

2. 实验任务

设计一个4位右循环一个1的环形计数器。

3. 实验原理

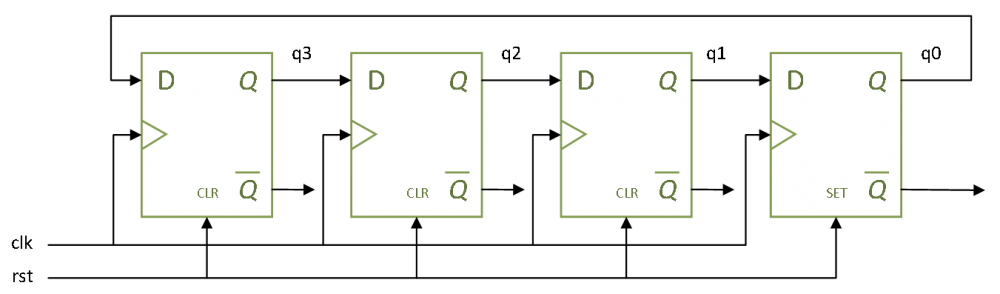

将移位寄存器的输出q0连接到触发器q3的输入,并且在这4个触发器中只有一个输出为1,另外3个为0,这样就构成了一个环形计数器。初始化复位时,给q0一个置位信号,则唯一的1将在环形计数器中循环移位,每4个时钟同期输出一个高电平脉冲。

4. 用CircuitJS仿真

5. Verilog HDL建模描述

用行为级描述带有复位的移位寄存器

用于Diamond仿真的程序清单 ring.v

module ring # ( parameter CNT_SIZE = 8 ) ( input wire clk,rst, //时钟和复位输入 output reg [CNT_SIZE-1:0] cnt //计数器输出 ); always@(posedge clk) if(!rst) cnt <= 8'b0000_0001; //复位初值 else cnt <= {cnt[0],cnt[CNT_SIZE-1:1]}; //右移循环计数 endmodule

仿真文件ring_tb.v

`timescale 1ns/100ps //仿真时间单位/时间精度 module ring_tb; reg clk,rst; wire [7:0] q; initial begin clk =0; rst =0; #20 rst =1; end always#10 clk =~clk; ring u1 ( .clk (clk), .rst (rst), .cnt (q) ); endmodule

6. 实验步骤

- 打开Lattice Diamond,建立工程。

- 新建Verilog HDL设计文件,并键入设计代码。

- 根据仿真教程,实现对本工程的仿真,验证仿真结果是否与预期相符。

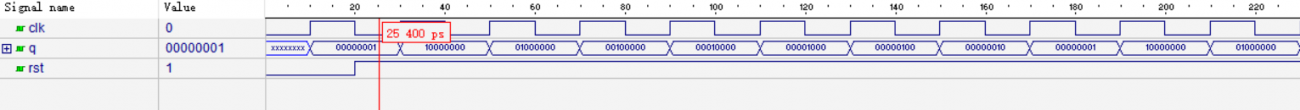

7. 仿真结果和实验现象