实验2.2 4位比较器

1.实验目的

- 熟悉和掌握FPGA开发流程和Lattice Diamond软件使用方法

- 通过实验理解和掌握比较器原理

- 学习用Verilog HDL描述多位比较器级联电路

2.实验任务

本实验的任务是描述4位的比较器电路,并用for语句和task语句实现比较器电路的级联效果。

3.实验原理

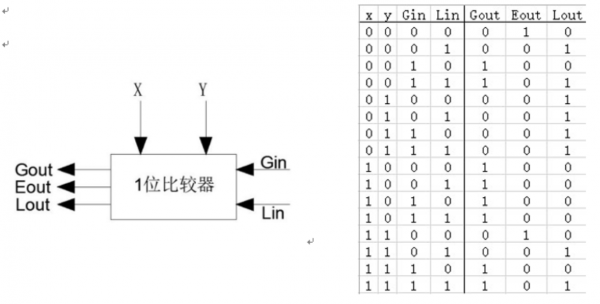

1位的比较器有如下性能:

- 如果X>Y或者X=Y且Gin=1,那么输出Gout为1;

- 如果X=Y且Gin=0和Lin=0,那么输出Eout为1;

- 如果X<Y或者X= Y且Lin=1 ,那么输出Lout为1 。

1位比较器原理图与真值表如下:

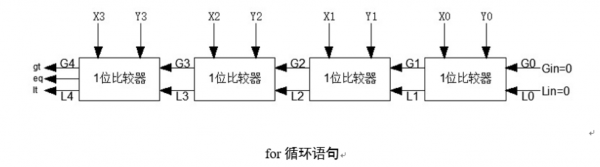

写一个如下图所示的4位比较器的Verilog程序,我们可以使用1位比较器的Verilog模块,然后使用4个模块实例语句创建这个顶层模块设计。若想增加比较器的大小,需要为增加的X和y的每一位写新的模块例化语句。在Verilog always块中使用for循环语句,就可以很方便地实现任意位比较器。然而,模块实例语句不能用在always模块中,但可以用在任务(task)中。

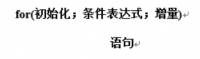

Verilog for循环语句的一般形式为

初始分配为循环变量设置初始值。当条件为真时,执行表达式,然后由语句描述的for循环实体执行。之后,增量更新,再执行一次表达式。for循环的实体一直循环执行,直到条件表达式的值为假。如果for循环的实体部分包含多条语句,那么应该放在begin和end之间。

初始分配为循环变量设置初始值。当条件为真时,执行表达式,然后由语句描述的for循环实体执行。之后,增量更新,再执行一次表达式。for循环的实体一直循环执行,直到条件表达式的值为假。如果for循环的实体部分包含多条语句,那么应该放在begin和end之间。

4.Verilog HDL建模描述

程序清单comp4.v

// -------------------------------------------------------------------- // >>>>>>>>>>>>>>>>>>>>>>>>> COPYRIGHT NOTICE <<<<<<<<<<<<<<<<<<<<<<<<< // -------------------------------------------------------------------- // File name : comp4.v // Module name : comp4 // Author : Step // Description : comp4 // Web : www.stepfpga.com // // -------------------------------------------------------------------- // Code Revision History : // -------------------------------------------------------------------- // Version: |Mod. Date: |Changes Made: // V1.0 |2015/11/11 |Initial ver // -------------------------------------------------------------------- module comp4 ( //INPUT x , y , //OUTPUT gt_led , eq_led , lt_led , empty ); //******************* //DEFINE INPUT //******************* input [3:0] x ; //4 bit input x (switch) input [3:0] y ; //4 bit input y (button) //******************* //DEFINE OUTPUT //******************* output gt_led ; //x is bigger than y output eq_led ; //x is equal to y output lt_led ; //x is smaller than y output empty ; //******************** //OUTPUT ATTRIBUTE //******************** //REGS reg gt_led ; reg eq_led ; reg lt_led ; //WIRE wire [10:0] empty ; //********************* //INNER SIGNAL DECLARATION //********************* //REGS reg [4:0] G =0 ; reg [4:0] L =0 ; reg [4:1] E ; //WIRES integer i ; //********************* //MAIN CORE //********************* always @ (*) begin for(i=0;i<4;i=i+1) comp1(x[i],y[i],G[i],L[i],G[i+1],L[i+1],E[i+1]); gt_led=~G[4]; //the led's default mode is lighted eq_led=~E[4]; //the led's default mode is lighted lt_led=~L[4]; //the led's default mode is lighted end task comp1( input x , input y , input Gin , input Lin , output Gout , output Lout , output Eout ); begin Gout=x&~y|x&Gin|~y&Gin; Eout=~x&~y&~Gin&~Lin|x&y&~Gin&~Lin; Lout=~x&y|~x&Lin|y&Lin; end endtask assign empty=11'b111_1111_1111; endmodule

五、 实验步骤

1.新建工程

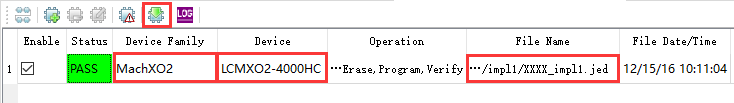

双击![]() 打开Lattice Diamond软件,点击File—New—Project新建工程,输入工程名称,指定工程保存目录,单击Next,选择设备如下:

打开Lattice Diamond软件,点击File—New—Project新建工程,输入工程名称,指定工程保存目录,单击Next,选择设备如下:

- Family选择MachXO2,

- Device选择LCMXO2-4000HC,

- Performance grade选择4,

- Package type选择CSBGA132,

- Operating conditions选择Commercial,

- Part Names为LCMXO2-4000HC-4MG132C。

- 选择综合工具Lattice LSE,完成。

2. 输入Verilog文件

点击File—New—File新建文件,类型选择Verilog Files,输入文件名称,选择保存路径,输入实验中的源代码后保存,编辑器会自动检查有无编辑错误,在下面的Output一栏会输出检查结果,如果有错误更正后重新保存直到没有报错为止。

3. 输入仿真文件

按照步骤(2)新建一个Verilog仿真文件,输入实验例程中仿真文件的代码后保存。在软件File List一栏中,右键单击“仿真文件”—Include for—Simulation,将文件设置为仿真文件(设置完成后文件图标的V会消失)。

4. 功能仿真

点击Tools选择Simulation Wizard或点击图标,按照仿真向导指示新建仿真工程,

- 输入工程名称,选择工程目录,选择Simulator为Active-HDL,

- Process Stage选择RTL,

- Add and Reorder Source:确认参与仿真的文件列表,Next

- Parse HDL files for simulation:软件会编译仿真文件,若报错需修改后重新仿真

- Summary:确认仿真工程信息,勾选Run simulator、Add top-level signals to waveform display和Run simulation,然后Finish

仿真软件会自动启动、运行仿真并显示仿真结果。查看仿真结果是否符合预期功能,如果不符合电路功能,则修改Verilog代码保存后,在Active-HDL中选择Design—Compile All 重新编译文件,编译通过后,在Simulation中重新开始仿真。

5. 综合

在Lattice Diamond软件的Process一栏,双击第一项Synthesize Design进行综合(确保仿真文件设置为simulation后不参与综合),综合结果会在下面的Output一栏中给出,如果有错误则修改Verilog文件后重新综合直至综合成功为止。

6. 分配管脚

7. 布局布线

双击Process一栏的Map Design和Place & Route Design完成FPGA内部的布局布线。

8. 生成配置文件

勾选并双击JEDEC File生成可下载的jed文件。