**这是本文档旧的修订版!**

FPGA的设计和实现

FPGA设计的各个阶段,FPGA厂商和EDA软件公司提供了很多优秀的EDA工具,尤其是FPGA厂商提供的集成开发环境。熟练掌握这些设计工具能够有效提高设计的效率,但是必须明白这些EDA软件只是一个工具,核心的FPGA设计流程是不变的。STEP小脚丫系列目前有支持Lattice和Intel-Altera的版本,未来将会开发基于Xilinx的FPGA芯片平台。

FPGA设计软件:

1. FPGA的开发流程

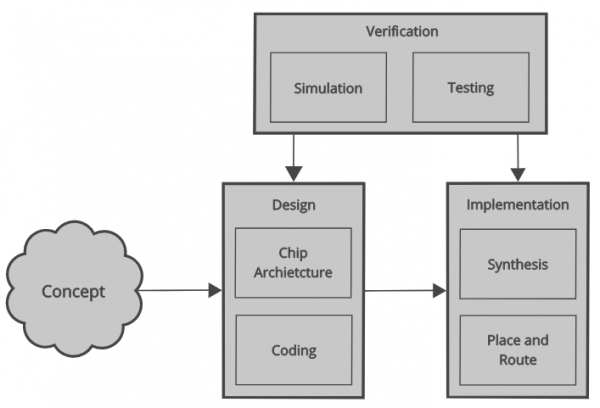

我们可以将FPGA的开发过程大致分为设计、验证和实现三个阶段。

- 在设计阶段,我们专注于将最初的概念或想法转换到实际的FPGA设备中。这通常包括设计芯片,或者把它分解成更小的块来形成一个完整的设计。然后,我们使用HDL语言或其他方法实现这些较小的块。

- 实现阶段采用我们的HDL设计,并将其转换为FPGA的编程文件。

- 验证过程提供给这两个过程。这包括测试和分析我们的设计和实现,以确保它能正确运行。

下图显示了开发生命周期中的各个阶段以及它们是如何相互关联的。

FPGA设计流程

1.1 FPGA设计过程

FPGA开发的第一阶段是设计。 我们通常从设计芯片开始。这涉及到将设计分解成许多更小的块来简化编码。 这可能是一个正式的过程,包括框图和与其他工程师的讨论。如果我们正在以专业的能力进行复杂的设计,这尤其可能。 类似地,如果我们在一个小项目中工作,我们可以使用伪代码来创建一个基本的设计思路。 下一阶段是创建我们设计的功能模型。我们通常使用一种主要的HDL语言来实现这个目的。 我们在这个过程中使用了两种主要的建模风格。这些通常被称为寄存器传输级别(RTL)和门级别。 当我们使用RTL方法时,我们描述了在FPGA中数据如何在触发器之间流动。 这意味着我们正在编写代码,从逻辑、RAM和状态机的角度明确描述FPGA的行为。 我们使用门级建模来定义不同预先存在的组件的互连。这些组件是集成FPGA元素的实例,如锁相环、lut或寄存器单元。 虽然我们在FPGA设计工作中使用了RTL,但大多数项目都混合使用了这两种方法。

关于FPGA设计更详细的介绍参见FPGA设计过程

1.2 FPGA验证过程

在编写了我们的设计模型之后,我们需要证明它是可行的。我们用于此的过程被称为验证。 我们的设计模拟的第一阶段。为此目的,我们创建了一个测试平台,它为我们的设计生成了许多输入。 然后,通过手工检查或自检代码,检查FPGA输出是否符合我们的预期。 我们可以在函数代码和发布地点和路由列表上重复这个过程。这是FPGA的一个模型,是在我们实现FPGA时由我们的软件工具创建的。这个模型包含了关于FPGA内部时序的信息,因此更能代表最终的实现。 通常,仿真是验证设计的主要过程。我们通常还通过硬件测试来补充这一点,以确保FPGA接口与所有外部电路符合预期。 然而,随着FPGA设计变得越来越复杂,其他技术也开始流行起来。 更现代的验证活动包括硬件在循环(HiL)和仿真。 在这两种情况下,这都涉及到在目标设备上运行代码,并向模拟软件反馈数据。这使得我们能够在设备上近乎实时地运行特定的、结构化的测试。 这是一个优势,因为post place和route netlist与函数代码相比模拟起来非常慢。用函数代码运行一个小时的模拟可以很容易地用一天或更多的时间运行一个post place和route netlist。

1.3 FPGA实现过程

一旦我们编写了代码并证明它是有效的,我们就需要在FPGA上编写这个设计。

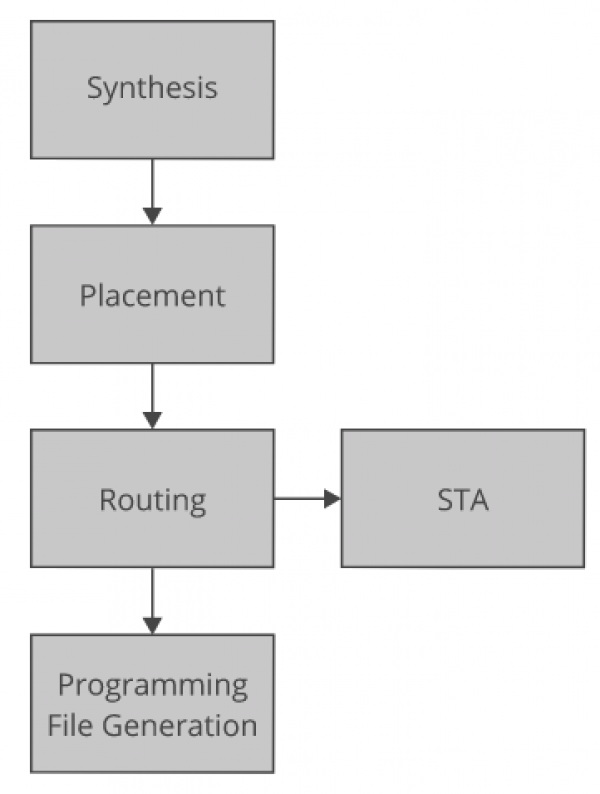

这个过程实际上包括三个阶段:合成、位置和路径以及编程文件生成。

合成过程将我们的功能代码转换成许多相互关联的门级宏。这些是内部FPGA单元的模型。

这个过程创建一个描述编程FPGA的内容的网表。我们可以把它想象成传统电路设计中的电路图。

在综合我们的设计之后,我们将网表映射到实际的FPGA资源。

第一部分是使用放置过程将宏映射到FPGA中的物理单元。当我们在传统的电子设计中设计pcb时,我们可以把这看作是把元件放在电路板上。

第二阶段包括在称为路由的过程中路由不同细胞之间的互连。这个过程相当于在PCB中布线。

为了满足我们设计的时间要求,通常需要多次运行场地和路线过程。地点和路线工具负责根据我们的配置安排这些多次运行。

作为地点和路线过程的一部分,我们还执行静态时间分析(STA)。该分析计算FPGA中所有时序路径的延迟,并确保我们的设计满足时序要求。

如果我们的设计失败了STA,那么我们不能保证FPGA将可靠地工作。当这种情况发生时,我们要么必须使用不同的设置再次运行实现流程,要么必须更改设计。

在实现过程的最后阶段是生成配置FPGA的编程文件。

下面的框图给出了整个FPGA实现流程的概述。

关于FPGA实现更详细的介绍参见FPGA实现过程

2. Verilog语言

在设计FPGA逻辑中有两种硬件设计语言(HDL)可以选择,一种是Verilog HDL,还有一种是VHDL,在我们的设计中选用普及率更广,更容易上手的Verilog,具体如何使用,可以参考文章末尾的几个PPT教程。

3. 代码规范

规范的代码风格一方面能体现你足够专业,另一方面也是最重要的一方面,代码的规范性有利于开发交流,让代码的可读性大大增强,也有利于降低代码的出错率。